[ keyword: EDA, SoC, プログラミング言語 ]

Forte,スケジューリングとリソース・アロケーションの同時実行・最適化により回路品質を改善したビヘイビア合成ツールを発売

ニュース 2013年6月24日

米国Forte Design Systems社は,スケジューリングとリソース・アロケーションの同時実行・最適化によって回路品質を改善したビヘイビア合成ツール「Cynthesizer 5」を発売する.例えば実際の24個の設計データに適用したところ,従来のツールを使ったときと比べて,面積が平均6%改善し,処理時間は平均25%短縮したという.

ここでスケジューリングとは,実現したい演算に対してクロック・サイクルを割り当て,各演算操作をどの時刻に実行するかを決定する処理である.リソース・アロケーションとは,演算器やメモリの共有を行い,演算回路の中で実際に使用するリソースを決定する処理である.従来のツールは,スケジューリングを行った後,リソース・アロケーションを行っていた.本ビヘイビア合成ツールは,これら二つの操作を同時に実行しながら評価・回路の改善を行うことで,より最適な回路が見つけやすくなったという.

また,本ビヘイビア合成ツールは消費電力最適化の機能を備えている.具体的には,ケーテッド・クロック回路やクロック・ツリーの最適化,ステート・マシンの状態割り当ての最適化,動作速度の遅いメモリ・ブロックの適用などにより,消費電力の低い回路を合成できる.例えば実際の6個の設計データに適用したところ,従来のツールを使ったときと比べて,消費電力を17.1%~63.1%低減できたという.

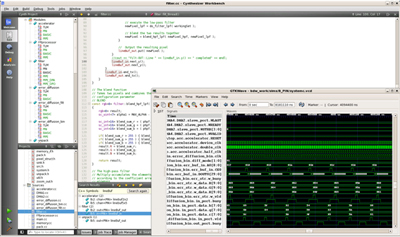

本ビヘイビア合成ツールには,入力言語であるSystemCの統合開発環境「SystemC IDE」が付属する.アプリケーション・ユーザ・インターフェースのフレームワークとして「Qt」を採用している.本開発環境には,SystemCのソース・コード・エディタ/デバッガ,波形ビューワ,サンプル・デザイン,オンライン・ドキュメントなどが含まれている.これとは別に,ソース・コードとリンクしながら合成結果をビジュアルに表示する解析ツールも提供する.

2013年夏ごろ(7月~8月)出荷を開始する予定.

図1 SystemC IDEの画面例

■価格 |

■連絡先 |