[ keyword: EDA, SoC, 開発手法 ]

Design Compilerが改版,フロアプラン機能を取り込んでタイミング収束の問題を緩和

ニュース 2010年3月30日

米国Synopsys社は,レイアウト設計との連携を強化した論理合成ツール「Design Compiler 2010」を発売した.フロアプラン(概略配置)機能を取り込むことにより,実際にレイアウトした場合と比較して,タイミングや面積の見積もり誤差を±5%程度に抑えた.

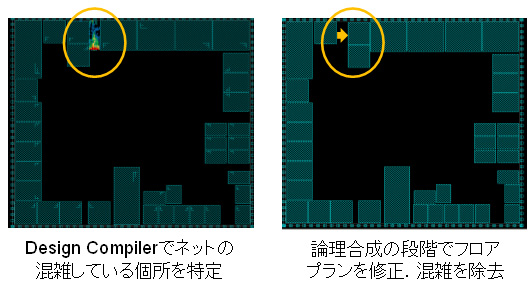

従来は,論理合成を行うRTL(Register Transfer Level)設計者とフロアプランやレイアウトを行うレイアウト設計者の間で,データの受け渡しや作業の手戻りが何度も発生していたという(いわゆるタイミング収束の問題).本論理合成ツールにはフロアプラン・ツール(IC Compiler-DP)が組み込まれている.論理合成の途中でフロアプランに手を加え,タイミングを改善したり,ネットの混雑を解消できる.また,フロアプラン情報はそのまま同社のレイアウト設計ツールに転送して,レイアウトの初期配置として使用できる.RTL設計者がフロアプランの決定に関与すれば,タイミングや面積の見積もり精度が向上し,結果として,論理合成とレイアウトに要する全体の期間を短縮できる.

さらに,マルチコア・プロセッサを搭載するコンピュータやサーバを利用して並列処理を行う機能も備える.例えば四つのCPUコアを搭載するプロセッサを利用する場合,回路を4分割して並列に論理合成を行う.論理合成に要する時間はシングル・プロセッサを使った場合の約1/2になるという.

[図1] フロアプランの画面例

[写真1] Design Compiler 2010についての説明を行う米国Synopsys社 Director, Product Marketing, RTL SynthesisのPriti Vijayvargiya氏

■価格 |

■連絡先 |