[ keyword: EDA, 開発手法, LSI ]

Mentor,C/C++入力のビヘイビア合成ツールに制御論理の生成機能と消費電力の最適化機能を追加

ニュース 2009年7月7日

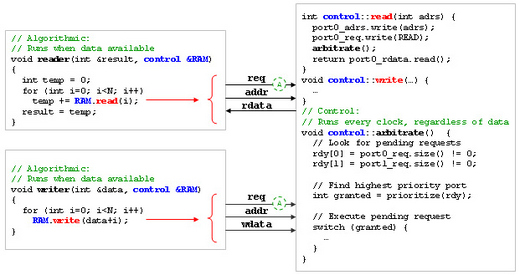

米国Mentor Graphics社は,同社のC/C++入力のビヘイビア合成ツール「Catapult C Synthesis」の機能を拡張した.従来は,主にアルゴリズムのC/C++記述から演算回路のRTL記述を生成していた.今回のバージョンでは,新たに制御手順やプロトコル処理などのC/C++記述から制御論理のRTL記述を生成できるようにした.ただし制御論理部のC/C++コードについては,同社が決めたモデリング・スタイルに合わせて記述する必要がある.

演算回路内部の演算器やレジスタ(パイプライン)の制御回路,および複数ブロック間のデータ・フロー制御のための回路は,従来から自動生成していたが,明示的に定義したC/C++コードから制御論理を生成できるようになったのは,今回が初めて.例えば,アービタやメモリ・コントローラ,バス・インターフェース,キャッシュ・コントローラなどの回路ブロックの設計に利用できる.

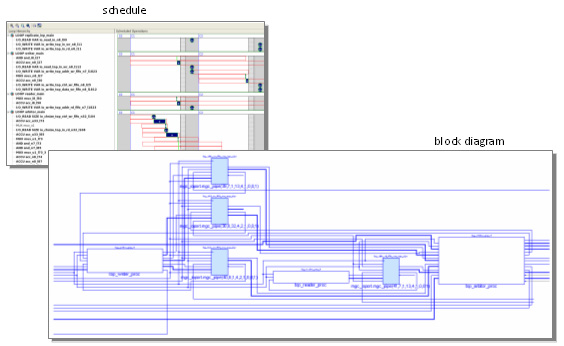

これにより,ビヘイビア合成を行う際に,演算処理部と制御論理部を一括して取り扱えるようなった.また,それぞれのC/C++モデルを組み合わせることにより,高速に回路全体の機能を検証できるという利点もある.

さらに,低消費電力設計のための機能として,ゲーテッド・クロック回路の挿入可能な領域を認識して自動挿入する機能や,クロック周波数や信号電圧を動的に変化させて消費電力を引き下げるための電力管理ブロックを生成する機能を搭載した.

加えて,検証を支援する機能として,C/C++モデルとRTLモデルの等価性をシミュレーションによって(動的に)検証する際に,ビヘイビア合成時の情報(論理的等価点やスケジューリングなどの情報)を利用してシミュレーション処理を高速化する機能も用意した.

[図1] メモリ・アービタの記述例(左側がアルゴリズム・ブロック,右側が制御ブロック)

[図2] メモリ・アービタ(図1)の合成結果

■価格 |

■連絡先 |