[ keyword: LSI ]

Altera,40nmプロセスで製造するFPGAとストラクチャードASICを発売

ニュース 2008年5月20日

米国Altera社は,40nmプロセスで製造するFPGA「Stratix IV」とストラクチャードASIC「HardCopy IV」を発売する.本FPGAファミリには,多くのメモリやDSPを持つ「Enhanced」と高速トランシーバ回路を備えた「GX」の二つのサブファミリがある.本FPGA用の設計データによって発注できるストラクチャードASICにも同じように,「Enhanced」と「GX」の二つのサブファミリを用意する.高速トランシーバ回路の搭載は,HardCopyファミリでは初めてである.

「GX」は,伝送速度が最大8.5Gbpsのトランシーバ回路と最大3.2Gbpsのトランシーバ回路を搭載する.また,最大4個のPCI Expressブロックをハード・マクロで搭載する.本ブロックでは,Gen1およびGen2,8レーン(x8)までのプロトコル処理を行うことが可能である.

電源電圧は,コア部が0.9V,I/O部が1.2V~3.0V.I/O電圧が3.0Vの場合,3.3VのLVTTL/LVCMOSとインターフェース可能である.

同社は同時に,Stratix IVに対応するFPGA開発環境「Quartus II 開発ソフトウェアv8.0」も発売する.v7.2と比べて,コンパイル時間を平均で22%,最大で50%短縮したという.また,インクリメンタル・コンパイル機能を利用する際に,パーティションを効率良く作成するためのグラフィカル・ツール「デザイン・パーティション・プランナ」を追加した.リソースの使用状況やパーティション間のタイミング情報を得ることができる.

Quartus II 開発ソフトウェア v8.0は,2008年6月3日よりダウンロードが可能となる.本FPGAファミリのES (エンジニアリング・サンプル)は,2008年第4四半期に出荷を開始する.

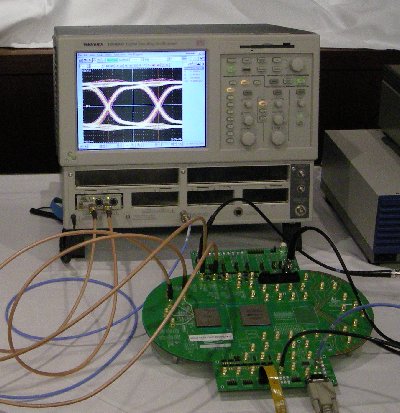

[写真1] Stratix IV GXのテスト・チップによる高速トランシーバ回路のデモンストレーション

[表1] Stratix IV GXの概要

EP4SGX70

EP4SGX110

EP4SGX230

EP4SGX290

EP4SGX360

EP4SGX530

ALM数

29,040

42,240

91,200

116,480

141,440

212,480

等価LE数

72,600

105,600

228,000

291,200

353,600

531,200

8.5Gbpsトランシーバ回路数

8

8,16

8,16,24

16,24

16,24

16,24,32

3.2Gbpsトランシーバ回路数

0

0

0,8,12

0,8,12

0,8,12

8,12,16

PCI Expressブロック数

1

1,2

1,2

2

2

4

合計メモリ容量(ビット)

7,370K

9,564K

17,133K

17,248K

22,564K

27,376

18×18乗算器数

384

512

1,288

832

1,040

1,024

PLL数

3

3,4

3,6,8

4,6,8,12

4,6,8,12

6,8,12

最大I/O数

368

368

736

864

864

904

[表2] Stratix IV E(Enhanced)の概要

EP4SE110

EP4SE230

EP4SE290

EP4SE360

EP4SE530

EP4SE680

ALM数

42,240

91,200

116,480

141,440

212,480

272,440

等価LE数

105,600

228,000

291,200

353,600

531,200

681,100

合計メモリ容量(ビット)

9,564K

17,133K

17,248K

22,564K

27,376

31,491

18×18乗算器数

512

1,288

832

1,040

1,024

1,360

PLL数

4

4

4,8,12

4,8,12

8,12

8,12

最大I/O数

480

480

864

864

960

1,104

■価格 |

■連絡先 |