[ keyword: LSI ]

Altera,同社の従来品と比べて集積度が2倍,消費電力が同程度のFPGAを発売,65nmプロセスで製造

ニュース 2006年11月9日

米国Altera社は,65nmプロセスで製造するFPGA「Stratix IIIファミリ」を発売する.本FPGAは,従来の90nmプロセスで製造するStratix IIと比べて,2倍の集積度と,25%の高速化を実現している.一方,消費電力は同程度にとどめたという.

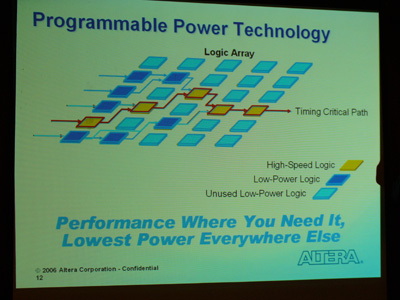

同社は,消費電力を抑えるために,「プログラマブル・パワー・テクノロジ」と呼ぶ技術を導入した.論理ブロックごとに,高速モード,低消費電力モード,未使用モードを選択できる.高速化のボトルネックになるクリティカル・パスに関連する論理ブロックには高速モードを,速度が重要でない論理ブロックには低消費電力モードを,使用していない論理ブロックには未使用モードを割り当てる.これにより,動作速度を低下させずに消費電力を抑えられるという.低消費電力モードではFPGAのコア電圧を制御している.また,未使用モードでは論理ブロックへのデータやクロックの供給を止めている.

本FPGAファミリには,汎用の「Logic」,多くのメモリやDSPをもち,ワイヤレス信号処理や画像処理に向く「Enhanced」,高速トランシーバ回路を備え,通信機器やストレージ機器に向く「GX」の三つのサブファミリがある.また,本FPGA用の設計データによって発注できるストラクチャードASIC(HardCopy)も用意する.

同社は同時に,Stratix IIIに対応するFPGA開発環境「Quartus II デザイン・ソフトウェア・バージョン6.1」も発売する.消費電力を考慮して,論理ブロックのモードを自動的に割り当てる「PowerPlay」と呼ぶ機能を備えている.また,論理ブロックのモードを個別に設定することも可能.

Quartus II デザイン・ソフトウェア・バージョン6.1は,2006年12月5日よりダウンロードが可能となる.Logic,Enhancedの各サブファミリのES(エンジニアリング・サンプル)は,2007年第3四半期に出荷を開始する.GX,HardCopyのサンプルの出荷時期については,後日発表するという.

[写真1] 「Stratix III」の外観

[写真2] 「プログラマブル・パワー・テクノロジ」により,消費電力を抑えることができるという

[表1] 「Stratix III」の特徴 (Logic) (Enhanced)

サブファミリ名

デバイス名

ALM数

等価LE数

合計

エンベデッド・

RAMビット数18ビット×18ビット

乗算器

(FIRモード)PLL数

Stratix III L

EP3SL50

19K

48K

1.8M

216

4

EP3SL70

27K

68K

2.1M

288

4

EP3SL110

43K

107K

4.2M

288

8

EP3SL150

57K

142K

5.2M

384

8

EP3SL200

80K

199K

7.4M

576

12

EP3SL340

135K

338K

17.2M

576

12

Stratix III E

EP3SE50

19K

48K

4.6M

384

8

EP3SE80

32K

80K

6.2M

672

12

EP3SE110

43K

107K

7.0M

896

12

EP3SE260

102K

254K

14.7M

768

12

■価格 |

■連絡先 |