[ keyword: SOC ]

LSI Logic,スイッチ機器や10Gbps伝送装置などに最適化した応用別マスタ・スライスを用意する0.11μmCMOS短納期ゲートアレイを発売

ニュース 2003年7月24日

米国LSI Logic社は,スイッチ機器や10Gbps伝送装置などの要求仕様に合わせたアプリケーション別のマスタ・スライスを用意する短納期ゲートアレイ(いわゆるStructured ASIC)「RapidChip」の新ファミリ「Xtreme」と「Integrator」の受注を開始した.マスタ・スライスには,あらかじめSerDes(serializer/deserializer)やメモリなどのハード・マクロが埋め込まれている.Xtremeは通信,ストレージ,コンピュータなどの特定用途向け,Integratorは汎用を想定したマスタ・スライスである.いずれも0.11μmルールのCMOSプロセスで製造する.7層の配線層のうち,4層を顧客が利用できる.

Xtremeの最大システム・クロック周波数は250MHz.LSI Logic社が提供する専用マクロについては,300MHz以上で動作するという.パッケージはフリップチップ.電源配線や高速信号配線を考慮して,専用のパッケージ基板を開発した.

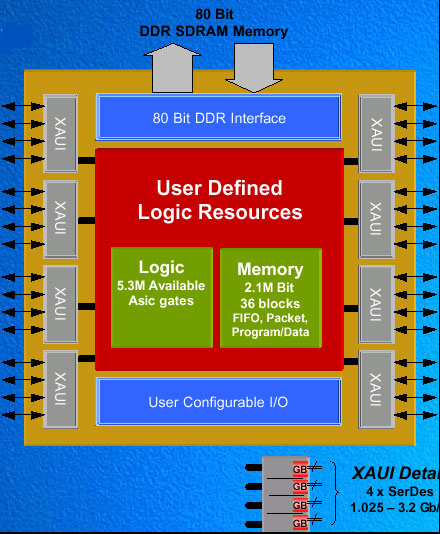

Xtremeのスイッチ機器向けマスタ・スライス(RC11XT432)の場合,32個のSerDes(伝送速度は1.025Gbps~3.2Gbps)と80ビット幅のDDR SDRAM用メモリ・インターフェースのハード・マクロが埋め込まれている.ユーザが使用できるゲート数は530万,メモリ容量は210万ビット.Fibre ChannelやPCI Express,Serial RapidIO,ギガビットEthernet,Serial ATAなどのスイッチ機器の開発に利用できるという.

また,10Gbps伝送装置向けマスタ・スライス(RC11XT531)の場合は,12個のSerDes(1.025Gbps~3.2Gbps),SPI4.2に準拠した18チャネルのOC-3/OC-12インターフェース(622Mbps~1.3Gbps),72ビット幅のDDR SDRAMメモリインターフェース,16チャネルのSFI4物理層インターフェース(644Mbps)のハード・マクロが埋め込まれている.ユーザが使用できるゲート数は500万,メモリ容量は220万ビット.10GビットEthernetコントローラやバックプレーン・ブリッジなどの機器の開発に利用できるという.

一方,Integratorの最大システム・クロック周波数は200MHz.埋め込まれているハード・マクロはメモリ・ブロックのみ.現在,サイズの異なる4種類のマスタ・スライスを用意している.ユーザが使用できるゲート数は290万~980万,メモリ容量は110万~540万ビット.メモリ・ブロックとして,2K×36ビット,1K×36ビット,512×36ビットの3種類のデュアル・ポートSRAMが埋め込まれている.パッケージはBGA.

開発環境として,RapidWorksと呼ばれるEDAツールを提供する.米国Tera Systems社と共同開発したRTLルール・チェッカ「RapidPRO」や米国Synplicity社と共同開発したフィジカル合成ツール「Amplify RapidChip」などが組み込まれている.

[図1] スイッチ機器向けマスタ・スライス(RC11XT432)の機能ブロック

■価格 |

■連絡先 |