プロセッサ最新テクノロジ2015 シリーズ6

tag:

2016年1月20日

SDSoC開発環境×C言語

CだけでHW/SWを全てコントロール ハード言語不要 組込みFPGAの新設計手法

これまで,プロセッサ上のソフトウェア開発とFPGA上のハードウェア開発はそれぞれ専門の技術者が別個に行うことが多かった.しかしザイリンクス株式会社(以下ザイリンクス社)のSoCであるZynqのようにプロセッサとFPGAを統合したデバイスの登場により,両技術者はより深く密接な関係をもつよう になっている.さらに,さまざまなアプリケーションでソフトウェアによる機能定義を実現しようとするソフトウェア・デファインの潮流から,これまで以上に ソフトウェア目線からのシステム開発の要求が高まっている.

今回は,ザイリンクス社の開発環境SDSoCについて,同社の黒田 成一氏にお話を伺った.

執筆:宮﨑 仁

|

|

ザイリンクス株式会社 グローバルセールス アンド マーケット ツール メソドロジー アプリケーション部 黒田 成一 氏 |

ソフトウェア・デファイン時代のFPGA設計 二極化していたHW/SW設計者が歩み寄り

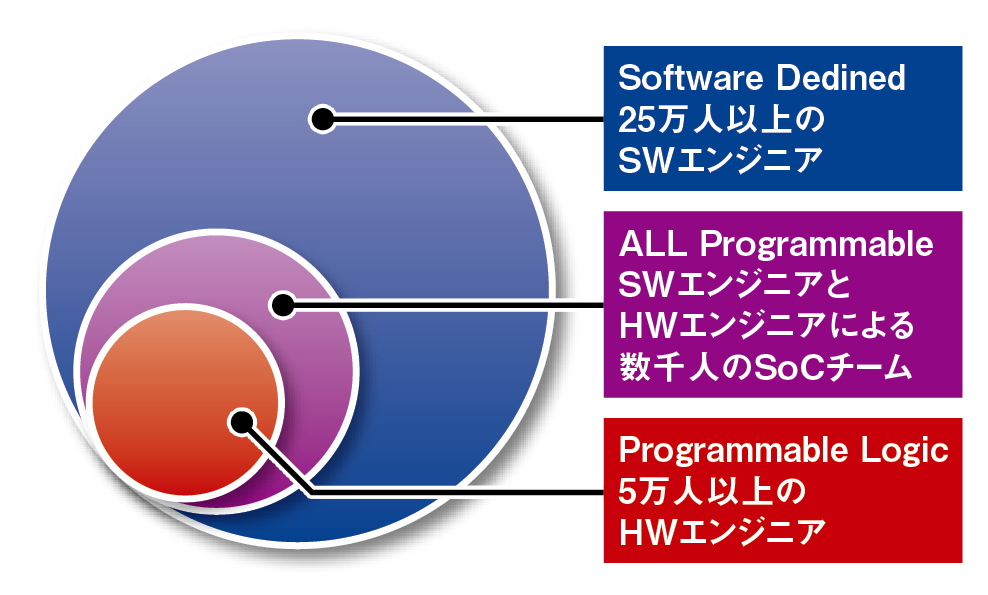

従来のプロセッサ開発は,アルゴリズムを実行するハードウェアが別途与えられており,それに依存せずに抽象度が高い記述が可能であった.また,プロセッサ の性能が向上すれば自然にシステム性能も向上し,ソフトウェア開発では,個別の性能追求よりは,汎用性や変更に対する柔軟性が追及されることが多かった. 一方でFPGA設計では,ハードウェア自体がプログラマブルで,HDL(ハードウェア記述言語)を用いてRTLなどの抽象度の低い記述が必要になる.そ のかわり,高速処理が可能になりFPGAを使いこなせるのはスキルをもつ特定の技術者に限られていた(図1).

図1 現在のエンジニアの配分 5年後にはこれらすべてがFPGA設計に関わるかも

この現状を踏まえてザイリ ンクス社では,ソフトウェアとハードウェアのプログラマブル性を統合して,あらゆる面でプログラマブルな新しいデバイス,テクノロジ,システムのプラット フォームを実現すべく, All Programmableというコンセプトを提唱している.代表的なデバイスとしては,ARMコアとFPGAを統合したZynq- 7000 All Programmable SoCがある.また開発環境のVivadoはHLx Editionが発表され,すべてのEditionに高位合成(Vivado HLS)が無償で含まれ,C言語のユーザにも十分使いこなせる環境を用意した.

● Software Definedとはソフト側がすべてを決める

最近ではシステムの柔軟性に対するより高度な要求として,Software Defined(ソフトウェア・デファイン)という言葉をよく聞くようになった. プロセッサの性能向上によって,これまでハードウェアで実現してきた機能が,次々にソフトウェアで置き換わることだ.これは,物理的なハードウェアを隠 蔽して,仮想的なハードウェアの上に抽象的なアプリケーションを実現すると言い換えることもできる.また,開発の立場から言えば,Software Definedとは,より多くのソフトウェア技術者が,アプリケーション開発と同等のセンスでプログラマブルなデバイスを活用するための新しい開発方法だ と言えるだろう.

● 開発環境は対象分野ごとにで分ける

実際の開発では,分野によってデバイスに対する要求やアプリケーションのセンスも異なっている.ザイリンクス社では,ネットワーク向けをSDNet, データ・センタ向けをSDAccel,組み込みシステム向けをSDSoCと具体的な分野ごとに開発環境を分けた. さらに,各分野でハードウェアを最適化する効果の大きいアプリケーションを次のように絞っている.

・画像処理[Video/Vision,I-Iot]

画像形式の変換や画像分析をハード化して,処理速度を向上.高解像度や高フレーム・レートを実現.

・センサ情報処理[ADAS]

カメラ画像をはじめ赤外線,レーダなど各種のセンサ入力を複合化させる.センサ・フュージョンや画像情報の繋ぎ合わせにより処理速度を向上.

・無線処理の向上[5G Wireless]

SDR(Software Defined Radio)による多彩なフォーマットへの対応やフィルタリング処理のハード化によって2×2,4×4MIMOへの対応.

・ネットワーク・システムの向上[SDN/NFV]

SDN(Software Defined Network)やNFV(Network Function Virtualization)で実現されるネットワーク環境下で,通信速度の確保(Wire Speed)やフロー単位でのサービス・プロビジョニングの最適化.

・ネットワーク・サービスの向上[Cloud]

クラウドのハードウェア・オフローディングにおけるAccelerationがきわめて重要となる.たとえば,検索エンジンや機械学習ではCPUやGPUに比べて数十倍のパフォーマンス/パワーを実現でき,データ・センタの消費電力の抑制に大きな効果がある.

2.従来の高位合成とは違う考え方のSDSoC

開発環境SDSoCは,C/C++やOpenCLによるソフトウェア記述から,ハードウェアを自動生成する高位合成ツールだ.だが,SDSoCは従来考えられてきた高位合成のイメージとは大きな違いがある.

(1) 必要部分だけを高速化する

従来の高位合成のイメージは,トップダウン設計の最上位からシステム全体をハードウェア化することを最終目標としてきた.だが,SDSoCはそれとは異なり,システム全体をソフトウェアとして設計する中で,処理速度などの性能面で必要な部分だけをハードウェア化する.これは,ソフトウェアの視線からみて,両者の優位性を最適化する自然な方法だ.

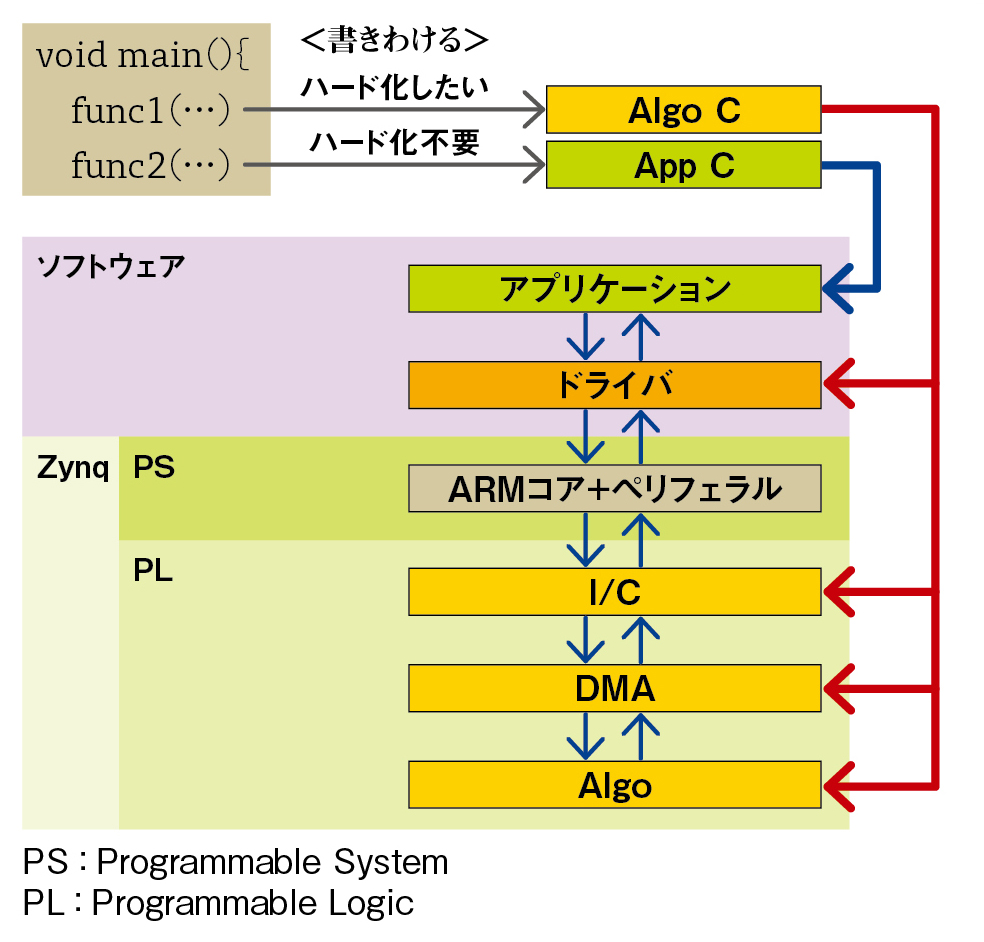

(2)つなぎも自動化─ハード化部分は関数として利用

もう一つは,単なるハードウェアの自動合成ではなく,ハードウェア部分をソフトウェア部品として利用するため,インタフェース部分やドライバ・ソフトまで一貫して自動合成する点だ(図2).これにより,ソフトウェア技術者にとって,特別に高速化されたライブラリ関数を呼び出して利用するのと同じことである.

図2 SDSoCによるハードウェアの自動生成

3.これからは,並列化を意識した ソフトウェアの書き方が役立つ

SDSoCを使ってHW/SWシステムを生成するのはとても簡単だ.開発者は通常のソフトウェア開発と同じように,Eclipseベースの統合開発環境の上で,C/C++でソース・コードを記述すればよい.高位合成などのツールは,統合開発環境の中にプラグインされており,自動的に必要な仕事をしてくれる.

記述したソース・コードの中にハードウェア化したい関数があれば,それを右クリックで選択するだけで,必要なハードウェアから関連ソフトウェアまでが自動的に生成される.まさに,ワン・クリックで関数を超高速化してくれる簡単ツールと言ってよい.

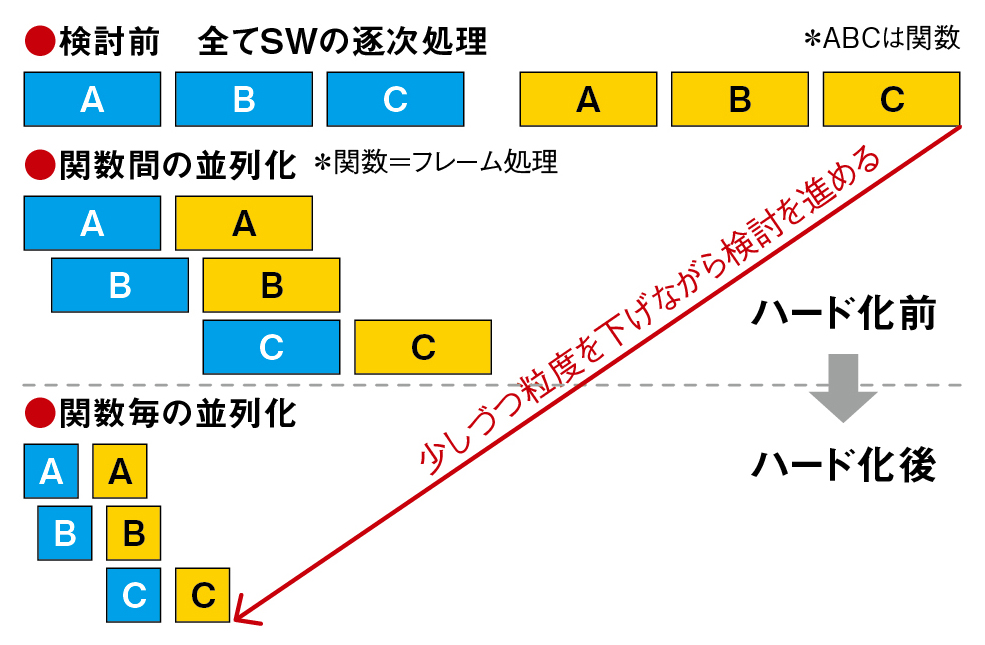

ただし,ソース・コードの記述は並列化を意識すべきだ(図3).元のソース・コードが直列的に逐次実行するものなら,生成されたハードウェアも直列的な回路になり,高速化の効果が上げにくい.ソース・コードのレベルで並列実行可能な部分やパイプライン処理が可能な部分を抽出し,それに適した構造の記述を行うことにより,SDSoCは効率の良い並列ハードウェアを生成してくれる.これは,ソフトウェア技術者にとって決してハードルが高い作業ではない.

図3 並列化を意識したソース・コードの構造

従来から,ハードウェア技術者はHDLを学ぶことで,このような並列化や回路アーキテクチャを意識した記述を身に付けてきた.ソフトウェア技術者がそれらを身に付けようとすれば,ハードウェア技術者と同じようにHDLを1から学ぶしかなかった.

だが,SDSoCで必要となる並列化はC言語の範囲内であり,HDLよりずっと容易である.しかも,このように並列化の観点で処理を分析・記述するセンスは,マルチコアを活用した純粋なソフトウェア開発にも役立つはずだ.組み込み開発にたずさわるソフトウェア技術者にとって,SDSoCは自らのスキルを磨き仕事の幅を広げる大きなチャンスと言えるだろう.

------------ 第6話 終了 ------------

----------------------------------------------------------------------------------------------

インターフェース誌 巻頭企画プロセッサ・メーカにテクノロジ・シリーズの

他の記事も読む

----------------------------------------------------------------------------------------------

この記事に関するお問い合わせ先

|

ザイリンクス株式会社 http://japan.xilinx.com/

〒141-0032 東京都品川区大崎1-2-2 アートヴィレッジ大崎セントラルタワー4階 j_info@xilinx.com