10nm技術のSRAMセルや48コアCPUの低消費電力技術などが登場 ―― VLSI Technology 2011 / VLSI Circuits 2011

●0.021平方μmの微小なSRAMセルを試作

それではVLSI 2011の注目発表を紹介しよう.はじめはVLSI Technologyの講演である.微細化をさらに追求したCMOS基本回路の試作発表が相次いだ.

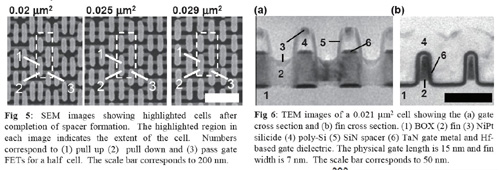

IBM社は,0.021平方μmと微小なSRAMセルを試作し,基本的な動作を確認してみせた(M.A. Guillornほか,講演番号4A-5).6トランジスタのSRAMセルとしては,これまでで最も小さい(写真6).製造技術は10nmと微細なSOI(Silicon on Insulator)CMOS技術とフィンFET技術.リソグラフィ技術に電子ビーム・リソグラフィ技術を導入して微細なパターンを形成した.メモリ・セルの寸法は0.10μm×0.21μmである.ゲート・ピッチとフィン・ピッチはいずれも50nmと短い.

写真6 SRAMセルの走査型電子顕微鏡写真(左)とトランジスタ断面の透過型電子顕微鏡写真(右)

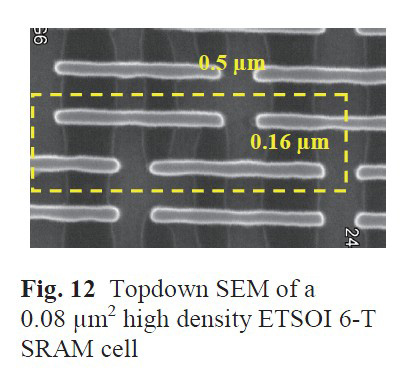

またIBM社とSTMicroelectronics社,米国GLOBALFOUNDRIES社,ルネサス エレクトロニクス,東芝の共同研究チームは,ゲート長が22nmと微細なSOI CMOS SoC(System on a Chip)技術を開発した(K. Chengほか,講演番号7-1).ETSOI(Extreme Thin SOI)と呼ぶ極薄チャネルのSOI技術を開発し,メモリ・セル面積が0.08平方μmという小さな6トランジスタSRAMセル・アレイを試作して動作を確認した.

トランジスタは高誘電率膜/金属ゲート(High-k/Metal gate)技術で作製している(写真7).高性能バージョン(HPタイプ)と低消費電力バージョン(LPタイプ)の2種類のトランジスタを用意した.nチャネル・トランジスタ/pチャネル・トランジスタのON電流(電源電圧は1V)はHPタイプが1150/1050μA/μm(OFF電流は100nA/μm),LPタイプが920/880μA/μm(OFF電流は1nA/μm)とかなり高い.

写真7 試作したSRAMセルの走査型電子顕微鏡写真

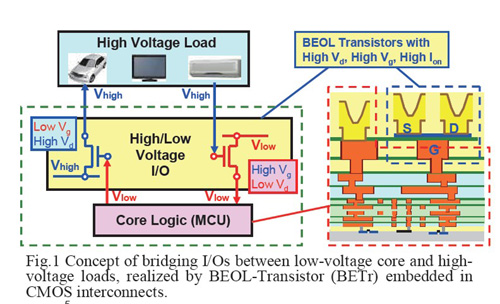

●高電圧入出力回路を標準CMOSデバイスに追加

ルネサス エレクトロニクスは,金属多層配線の上に高耐圧トランジスタを作製する技術を開発した(K.Kanekoほか,講演番号6B-3).この技術を利用すると,標準CMOSプロセスで製造したマイコンなどの低電圧ロジック回路に,高電圧の入出力回路を追加できるようになる(写真8).

写真8 標準CMOSプロセスのマイコンに高電圧入出力回路を追加

トランジスタの材料は化合物半導体のインジウム・ガリウム酸化亜鉛(InGaZnO)である.金属多層配線に標準的に使われている銅をゲート電極としている.ゲート絶縁膜は窒化シリコン膜.

●メニイコア・プロセッサの消費電力管理技術を発表

続いてVLSI Circuitsの講演である.消費電力を低減したプロセッサや周囲のエネルギーを取り込んで動かす微小電力回路など,電力に関連した技術発表が少なくなかった.

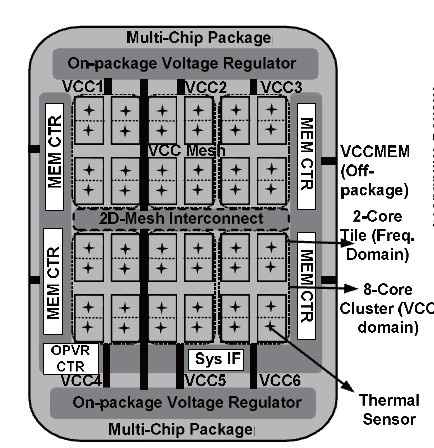

Intel社と米国Purdue Universityの共同研究チームは,48個のx86 CPUコアを内蔵するメニイコア・プロセッサを試作し,メニイコア・プロセッサ向けの消費電力技術を評価した(写真9,S. Digheほか,講演番号24-1).メニイコア・プロセッサではCPUコアの性能ばらつきが全体の演算処理性能を左右する.特に問題となるのが,最も性能の低いCPUコアである.リーク電流が高かったり,動作周波数が低かったりするCPUコアだ.

写真9 48個のx86 CPUコアを内蔵するメニイコア・プロセッサの内部ブロック図

そこでメニイコア・プロセッサでは,CPUコアごとの性能ばらつきを考慮した電源電圧制御と動作周波数制御が重要になる.試作した48コア・プロセッサでは,8個のコアを1個の電源電圧ドメインでまとめた8個の電圧ドメインと,24個のコアを1個のクロック周波数でまとめた2個の周波数ドメインに分け,電源電圧と動作周波数を最適にマッピングした.その結果,最大動作周波数が800MHzの場合の消費電力を最大で14.5%低減できた.