無償ツールで実践する「ハード・ソフト協調検証」(5) ―― テスト・プログラムの作成とBFMのコードの生成

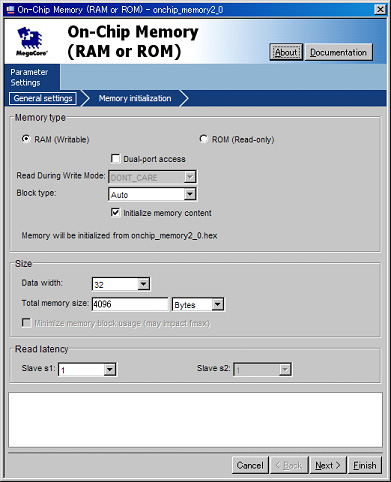

すると,図12のような画面が表示されるので,ここでも[Finish]ボタンをクリックします.

図12 On-Chip Memory を追加したときの画面

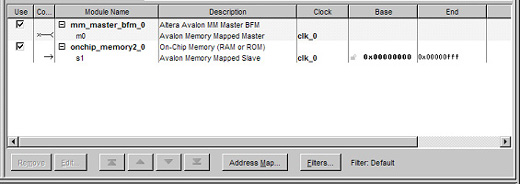

二つのIPコアを追加すると,図13のように右側の窓の上が「mm_master_bfm_0」,下が「onchip_memory2_0」になります.

図13 BFMとOn-Chip Memory (RAM or ROM)を追加したときの画面

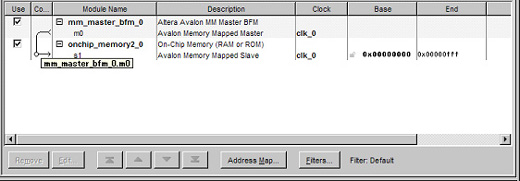

ここで左側から2カラム目にマウスを移動すると図14のようになり,ここでマウスをクリックします.

図14 BFMとOn-Chip Memoryを接続する画面

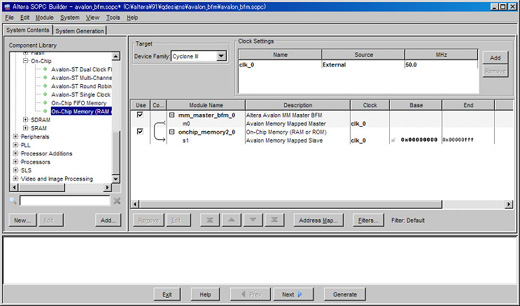

すると,図15のように二つのIPコアが接続されます.

図15 BFMとOn-Chip Memoryを接続したあとの画面

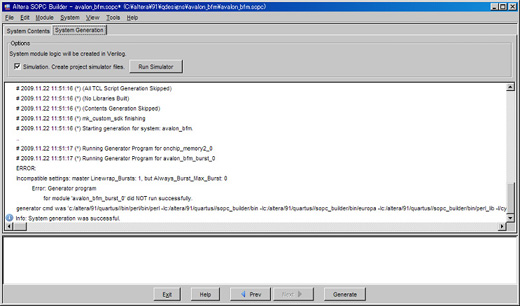

これで二つのIPコアが接続できたので,Verilog HDLコードを生成します.Verilog HDLコードは,図15の右下の[Generate]ボタンをクリックすることで生成できます.[Generate]ボタンをクリックすると,「Save changes to avalon_bfm.sopc」というウィンドウが表示されるので,[Save]ボタンをクリックします.そうすると,図16のように「System Generation」ペインに切り替わり,Verilog HDLコードが生成されます.なお,「System Generation」ペインに切り替わったら,「Simulation : Create project simulator files」をチェックしてください.チェックすることでModelSim用のプロジェクト・ファイルを生成します.このModelSim用のプロジェクト・ファイルは次回のシミュレーションで使用します.

図16 Verilog HDLコードを生成したあとの画面

(第6回へ続く)

Verification Enginnerの戯言

http://blogs.yahoo.co.jp/verification_engineer