無償ツールで実践する「ハード・ソフト協調検証」(5) ―― テスト・プログラムの作成とBFMのコードの生成

11.SOPC Builderを使ってVerilog HDLコードを生成する

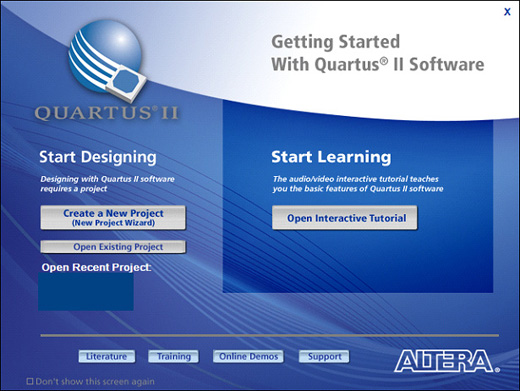

SOPC Builderを利用してVerilog HDLコードを生成します.Altera社のFPGA開発環境であるQuartus IIを起動し,図6のようなプロジェクトを指定するウィンドウ画面が表示されたら,「Create a New Project」をクリックします.

図6 Quartus IIのプロジェクトを指定する画面

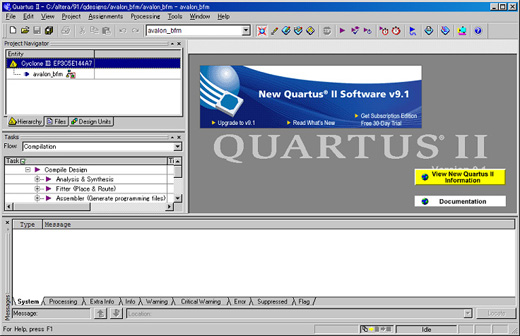

ここで出てくるウィンドウに従って,プロジェクトをストアするディレクトリとプロジェクト名を指定します.ここでは,ディレクトリには「c:\altera\9.1\qdesigns\avalon_bfm」を,プロジェクト名には「avalon_bfm」を指定します.すると,図7のような画面が表示されます.

図7 avalon_bfmプロジェクトを作成したときのQuartus IIの画面

図7の右上にある赤の点線の四角の部分をクリックするとSOPC Builderが起動し,図8のような画面が表示されます.

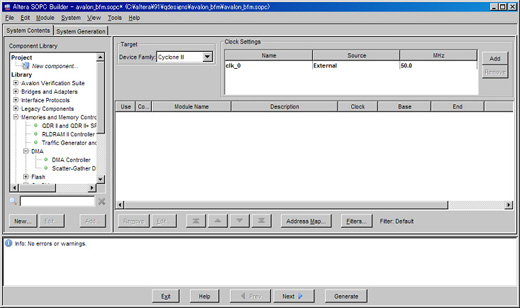

図8 SOPC Builderの初期画面

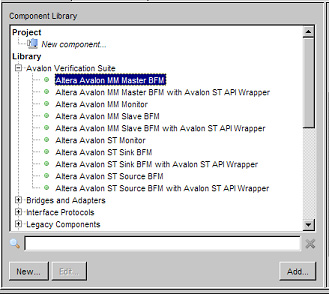

図8において左の窓の「Avalon Verification Suite」をクリックし,図9の一番上の「Aletra Avalon MM Master BFM」を選択し,右下の[Add]ボタンをクリックします.

図9 Altera Avalon MM Master BFMを選択した画面

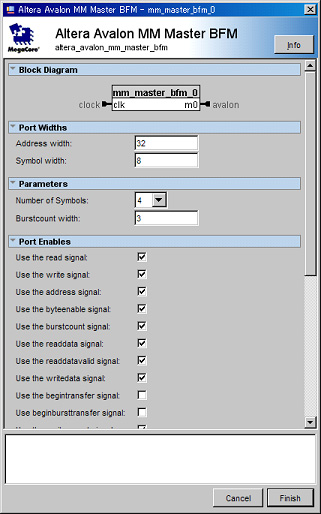

すると,図10のような画面が表示されるので,ここでは[Finish]ボタンをクリックします.

図10 Altera Avalon MM Master BFMを追加したときの画面

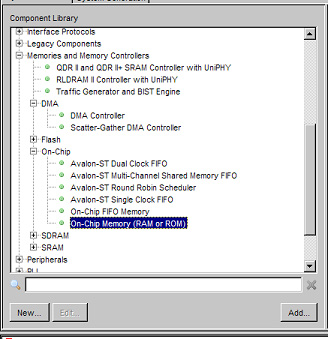

次に図11の「Memories and Memory Controllers」→「On-Chip」→「On-Chip Memory (RAM or ROM)」を選択し,[Add]ボタンをクリックします.

図11 On-Chip Memory (RAM or ROM)を選択した画面