無償ツールで実践する「ハード・ソフト協調検証」(3) ―― Avalonインターフェースと検証用モデル

6.SOPC Builder

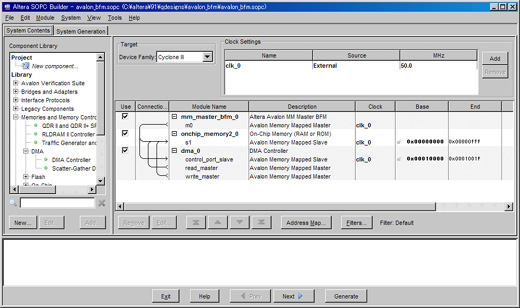

Altera社はSOPC Builderというツールを用意しています(図5).これは,CPUコアや内部メモリ・ブロック,外部メモリ・インターフェース・ブロック,PCIインターフェース・ブロック,PCI Expressインターフェース・ブロック,USBインターフェース・ブロック,Ethernetインターフェース・ブロックなどを同社のFPGAに簡単に実装するためのツールです.

図5 SOPC Builderの画面例

SOPC Builderは同社のFPGA開発環境「Quartus II」から呼び出すツールで,必要な機能をユーザがドラック&ドロップで選択し,FPGA全体の回路構成を設定するためのものです.SOPC Builderを使えば,設定した回路構成の情報から自動的にHDLコードを生成できるので,ユーザはHDLコードを1行も書かなくてもFPGAを設計できます.ただし,SOPC Builder内に用意されているIPコアだけで必要な機能を実現できない場合は,何らかの方法でユーザが不足している回路ブロックのHDLコードを記述する必要があります.

SOPC Builderは,各IPコアのアドレス・マップを割り当てるだけでなく,アドレスの重複や未接続部のチェックなどを自動で行います.このため,人手でコードを作成するときに生じがちなケアレス・ミスがなくなります.また,IPコア間を接続するための内部バスのHDLコードを自動的に生成します.

SOPC Builderを使ってベース・システムを構築し,正しく動くことを確認したあとで機能の追加が発生することがあります.その場合,ユーザはドラック&ドロップでIPコアを追加し,IPコアのピンを必要な場所に接続し,アドレス・マップを決めるだけで機能追加の作業は終わりです.同じように不必要な機能を削除すると,その部分に相当するHDLコードが自動的に削除されます.

このように,SOPC BuilderはAltera社のFPGAに回路を実装するためには非常に有用なツールです.従来,各インスタンス間を接続するHDLコードを人手で記述していたことを考えると,SOPC Builderによる回路構成の作成は画期的です.HDLコードの自動生成により回路記述の生産性が向上するだけでなく,回路記述の品質もよくなります.

7.Avalonインターフェース

Avalonは,SOPC Builderで提供している内部バス・インターフェスです.Avalonインターフェースの仕様書は,下記のWebサイトからダウンロードできます.

・Avalon Interface Specifications ver.1.2,Apr. 2009,485Kバイト

Avalonインターフェースには,大きく分けて二つのインターフェース仕様が定義されています.

一つ目はAvalon Memory-Mappedインターフェース(以下,Avalon-MMインターフェースと呼ぶ)です.Avalon-MMインターフェースは,メモリ・マップされたアドレス空間において,マスタ(Master)からスレーブ(Slave)に対してリードあるいはライト・サイクルを発行します.Avalon-MMインターフェースは,一般的なバス・インターフェースと同じ仕様です.

二つ目の仕様はAvalon Streamingインターフェース(以下,Avalon-STインターフェースと呼ぶ)です.Avalon-STインターフェースでは,Avalon-MMインターフェースとは違ってデータの流れは1方向です.データは必ず,ソース(Source)からシンク(Sink)に流れます.あるモジュールがAvalon-STインターフェスをサポートするということは,入力の場合はAvalon-ST Souceになり,出力の場合はAvalon-ST Sinkになります.Avalon-STインターフェースは,画像やデータをストリーム・データとして扱うときに利用すると便利です.

SOPC Builderでは,Avalon-MMインターフェースやAvalon-STインターフェースに対応したIPコアを多く利用できます.もし,SOPC Builderに登録されているIPコアでは対応できない処理を行うときは,ユーザがAvalonインターフェースに対応したIPコアを開発し,SOPC Builderに登録すれば,登録済みのIPコアと同じようにSOPC Builderの中で利用できます.

では,Avalonインターフェースに対応したIPコアを開発するにはどうすればよいのでしょうか? 一般的なIPコア開発と同じですが,Avalonインターフェース部については,その仕様を満足するかどうかを検証する必要があります.そのためのモデルとして,Altera社は「Avalon Verification IP Suite」というAvalon BFM(検証用のバス・ファンクショナル・モデル)を提供しています.このAvalon BFMを利用することで,ユーザはAvalonインターフェース部を持つIPコアをスムーズに検証できます.