FPGAベンダがストラクチャードASIC事業の成功をアピール ――Electronic Design and Solution Fair 2007

2007年1月25日~26日,パシフィコ横浜(神奈川県横浜市)にて,LSI設計やEDA技術に関連する展示会「Electronic Design and Solution Fair 2007」が開催された(写真1).日本アルテラは,ストラクチャードASIC「HardCopy」と「HardCopy II」の採用事例として,ソニーのビデオ機器などの搭載基板を展示した.

[写真1] Electronic Design and Solution Fair(EDS Fair)2007の会場風景

2007年1月25日~26日,パシフィコ横浜で開催された.

●ソニーや三洋,横河などがAltera社のストラクチャードASICを採用

日本アルテラは,ストラクチャードASIC「HardCopy」と「HardCopy II」の採用事例として,ソニーのビデオ機器や三洋電機のプロジェクタ,横河電機のプラント制御システム,メディアグローバルリンクスのディジタル放送用コンバータなどの搭載基板を展示した(写真2).ストラクチャードASICとは,あらかじめ用途ごとに異なるハード・マクロを用意し,ユーザごとに製作する配線層のマスクの枚数を減らしてコストダウンを図ったASICである.

HardCopyは,同社のFPGAファミリである「Stratix」と同等の論理ブロックやハード・マクロ(PLLやメモリ,I/Oバッファなど)を持ち,ピン互換性がある.同社では,試作や少量の初期ロットにはStratixを利用し,量産時にHardCopyに切り替える方法を提案している.

[写真2] ストラクチャードASICの採用事例

ソニーのHDビデオ・カメラ(「PDW-F350」と「PDW-F330」)やHDビデオ・デッキ(「PDW-F70」と「PDW-F30」)の搭載基板.左の基板は開発時のもので,FPGA(EP1S60とEP1S40)を使用している.右の基板は量産時のもので,FPGAがストラクチャードASIC(HC1S60とHC1S40)に置き換わっている.

●ビヘイビア合成と連携したサイクル精度の協調設計ツール

インターデザインは,ハードウェアとソフトウェアの協調設計を支援するサイクル精度のシミュレータを参考出展した(写真3).半導体理工学研究センター(STARC)が開発したバジェット追加技術を利用して,時間制約情報を追加したSpecCファイルを生成する.また,NECシステムテクノロジーのビヘイビア合成ツール「CyberWorkBench」が出力するハードウェアのモデルを取り込んで,ソフトウェアとハードウェアをサイクル精度でシミュレーションできる.本シミュレータは,同社のシステム・レベル・シミュレータ「VisualSpec」を基に開発した.

バジェット追加技術とは,ソフトウェアのC言語ソース・コードを実行する際に必要な命令サイクル数を算出し,その時間制約情報を追加したモデルを生成する技術である.なお,同社は,すでにバジェット追加技術を利用したSystemCシミュレータ「FastVeri」を製品化している.

対応しているCPUモデルはARM7,ARM9,およびTX49.現在,MIPS 5Kfに対応させるためのライブラリも作成中.製品化の時期は未定.

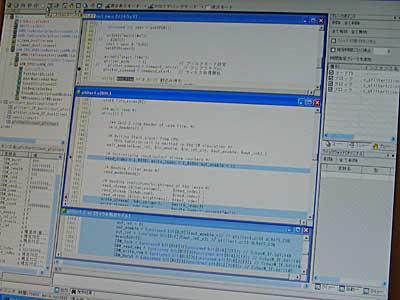

[写真3] シミュレータでステップ実行のデモンストレーションを行っているところ(クリックすると拡大)

画面中の,上部にあるウィンドウがCソース・コードで記述されたソフトウェア・モデル,中央にあるのがNECのBDL(Behavioral Description Language)記述で表現されたハードウェアのビヘイビア・モデル,下部にあるのが生成されたサイクル精度のハードウェア・モデルである.

●浮動小数点を固定小数点に自動変換する設計ツール

礎デザインオートメーションは,浮動小数点数による処理を固定小数点数による処理に変換するツール「FP-Fixer ver.1.0」を展示した(写真4).ANSI-Cで記述された入力ファイルの浮動小数点数に対してシミュレーションを実施し,各数値を観測する.そして,その情報に基づいてビット幅を確定し,固定小数点型のANSI-Cコードに変換して出力する.ビット幅の精度や制約は任意に指定できる.また,複雑な評価を行うための評価関数も用意されている.Windows環境およびLinux環境で動作する(Windows環境ではGNUのCコンパイラ「MinGW」を使用).すでに出荷を開始している.

将来的には,出力ファイルとしてSystemCコードやDSP向けCコードを出力することも計画しているという.

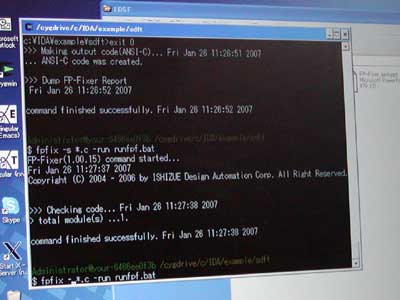

[写真4] FP-Fixerを実行しているところ

●CoWareとTensilicaが協調設計ツール用ライブラリを共同開発

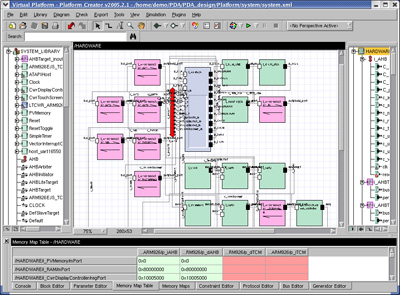

米国CoWare社と米国Tensilica社は,Tensilica社のプロセッサ・コア(Xtensa,Diamond Standard)に対応したProcessor Support Package(PSP)と呼ばれるライブラリを共同開発した.PSPは,CoWare社のハードウェア・ソフトウェア協調設計ツール「Platform Architect」において使われるSystemCのライブラリである.Platform Architectを用いると,SystemCなどによるシステムのアーキテクチャ設計やシミュレーション,性能解析,デバッグなどが行える(写真5).本ライブラリの開発により,Platform Architect上でTensilica社のプロセッサ・コアを用いたシステム設計が可能となった.

[写真5] CoWare社の開発ツール「Platform Creator」の画面

●500以上のI/Oを接続できるSpartan-3ボード

エスケーエレクトロニクスは,Xilinx社のSpartan-3(XC3S5000-4FF1156)を搭載したプロトタイピング・ボード「M-22」を展示した(写真6).本ボードの上部にアドオン・ボードを,下部にベース・ボードを接続して機能を拡張できる.ベース・ボードとは,最大544本のI/Oを介して接続する.アドオン・ボードとは,最大191本のI/Oを介して接続する.このI/Oには,SSTLインターフェースの信号線を最大109本,LVDSインターフェースの信号線を最大38ペア接続できる.2007年1月から出荷を開始している.

また,本製品を含むプロトタイピング・ボード・シリーズ「Accverinos」と合わせて使用できる制御用ソフトウェアを開発した.回路のマッピングやクロック生成,コンフィグレーション・ファイルのFPGAへのダウンロードなどを一つの画面上で制御できる.本ソフトウェアは,2007年春ごろから提供を開始する予定.

[写真6] プロトタイピング・ボード「M-22」の外観

●無線通信規格の物理層信号を解析するソフトウェア

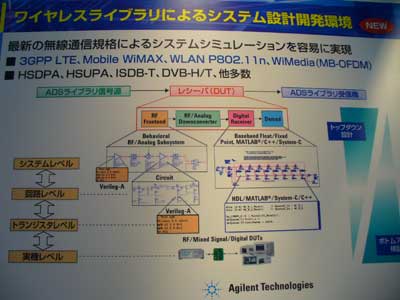

アジレント・テクノロジーは,各種無線通信規格の物理層の信号に対応する解析ソフトウェア「ワイヤレスライブラリ」を展示した(写真7).被測定デバイスへ信号を送出するソフトウェアと,被測定デバイスから出力された信号を解析するソフトウェアから成る.

信号源として,3GPP LTEやモバイルWiMAX,WLAN P802.11n,WiMedia(MB-OFDM)などのテスト信号を用意する.理想的なベースバンド信号だけでなく,実機がやりとりするデータを加えた変調信号も生成できることが特徴.

本ソフトウェアは,同社の高周波回路設計ツールである「ADS(Advanced Design System)シミュレータ」に組み込んで提供される.ADSシミュレータをパソコンにインストールすると,パソコン内に信号源と被測定デバイス,受信機のモデルを構成できる.ユーザはこの被測定デバイスをシステム・レベル,回路レベル,トランジスタ・レベル,実機レベルでシミュレーションできる.

[写真7] ワイヤレスライブラリに関する展示

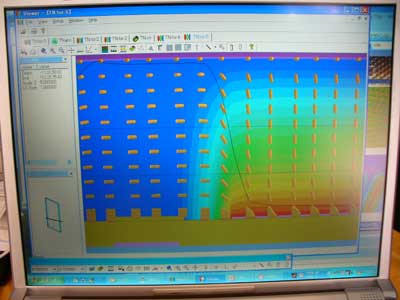

●液晶分子の動きを模擬できる3次元物理シミュレータ

ジーダットは,同社が国内販売代理店を務める韓国DAOU XILICON社の3次元物理シミュレータ「ExpertLCD」を展示した(写真8).アクティブ・マトリクス液晶ディスプレイの液晶分子の動きをシミュレーションして,ディスプレイの色合いや明るさ,視野角,コントラスト比などの情報を出力する.

3D FEM(有限要素法)解析を用い,電界分布と液晶分子の向きを計算する.本シミュレータに画素構造(マスク・データ,厚み,材料)と材料特性(電極の抵抗,光の屈折率),電極に加える電圧の三つのパラメータを与えて,液晶分子の振る舞いをシミュレーションする.その結果として,ディスクリネーション(光漏れ)やバックライト光の透過率,光の視野角特性,コントラスト,バックライトのちらつき具合,V-Tカーブ,ガンマ補正のための基礎情報が得られる.

液晶分子は,分子の向きによって画素中の誘電率が変わる.同社のシミュレータはこの画素容量の変化も計算できる.そのため,Spiceなどの回路シミュレータを利用すると,同一パネル上の各画素における液晶駆動波形を確認できる.

[写真8] ExpertLCDの実行画面