車載機器やネットワーク家電など,具体的な応用機器をターゲットとした開発・評価環境が続々 ――第9回 組込みシステム開発技術展(ESEC)

2006年6月28日~6月30日,組み込みシステム開発に関する展示会「第9回 組込みシステム開発技術展(ESEC)」が,東京ビッグサイト(東京都江東区)にて開催された(写真1).車載機器やネットワーク家電など,具体的な応用機器をターゲットとした開発環境や評価キット,リファレンス・デザインなどのデモンストレーションがあちらこちらで行われていた.

[写真1] 第9回 組み込みシステム開発技術展の会場風景

2006年6月28日~6月30日に東京ビッグサイトにて開催された

●アタッシュ・ケース一つでLIN 2.0の評価を行えるキット

NECエレクトロニクスは,アタッシュ・ケース型の「LIN 2.0評価キット」のデモンストレーションを行った.マスタ・ノードやスレーブ・ノードのボードだけでなく,ライトやサイド・ミラー,ドアの動きが視覚的に理解できるように模型が組み込まれている(写真2).自動車メーカや電装メーカにおけるLIN 2.0の評価のほか,大学や専門学校などにおける学習教材としての需要を見込んでいる.顧客からの要望があれば外販していきたいという.

マスタ・ノードとして,同社の32ビット・マイコン「V850ES/FJ2」を搭載した評価ボードを用いている.また,スレーブ・ノードには,LIN 2.0トランシーバ回路や電源回路を内蔵した8ビット・マイコン「uPD78F8006H」を搭載している.本評価キットはスレーブ・ノードを五つ備えており,左右のドアの開閉の検出,ヘッド・ライトやウィンカ,ブレーキ・ランプ,サイド・ミラーの動作を制御する.スイッチにより,10ms~990msの間でフレーム・スロット時間を設定できる.なお,本評価キットはLINの部分のみで,CANなどのネットワーク機能は備えていない.

[写真2] LIN 2.0評価キット

操作パネルにはフレーム・スロット時間設定用スイッチのほか,ウィンカ,ヘッド・ライト,ブレーキ・ランプ,ミラー操作,ハザード・ランプを動作させるためのスイッチなどが付いている.デモンストレーションでは,LIN-USBインターフェース・モジュールを用いて,LINバス上のデータをパソコンでモニタしていた

●DLNA対応ネットワーク家電のための開発環境

フリースケール・セミコンダクタ・ジャパンのブースでは,「DLNA(Digital Living Network Alliance)」に対応したディジタル家電機器の開発環境のデモンストレーションが行われた(写真3).DLNAはパソコンや家電などの間でディジタル・コンテンツを共有するためのインターフェース規格.2004年に最初のガイドラインが策定された.

本開発環境は,米国Freescale Semiconductor社のCPU評価ボード「MPC8349E-mITX」,米国Wind River社のソフトウェア開発環境「Wind River Linux Platform」,デジオンのメディア・サーバ用ミドルウェア「DiXiM」からなる.ディジタル家電やパソコンの開発,また将来的には携帯機器のDLNA対応アプリケーション開発における需要を見込んでいる.

デモンストレーションでは,ハード・ディスク装置に格納された四つのMPEG-2の動画データを,それぞれ20Mbpsの伝送速度で同時にネットワークを介して再生用のクライアント機器(DMP:digital media player)に送信していた.

[写真3] DLNA対応アプリケーションの開発プラットホーム

写真では二つの映像しか見えないが,実際のデモンストレーションでは四つのMPEG-2データを同時にクライアント機器へ送出していた

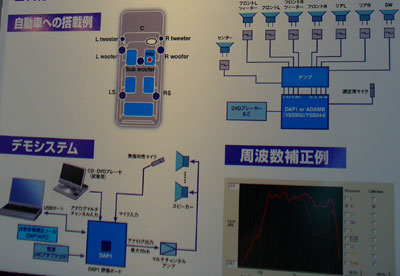

●最大7.1チャネルに対応した自動車向け自動音場補正システム

ヤマハは,自動車向け自動音場補正システムを展示した(写真4).車内の前後左右,センタなどに搭載されている最大7.1チャネルのスピーカの音を,特定の位置に座る人に最適な特性となるように補正する.主な調整項目として,音の遅延時間(到達距離によって生ずる位相差の補正),レベル(到達距離によって生ずる音圧の補正),周波数(スピーカのもつ周波数特性の補正)の三つがある.

この自動音場補正システムは,同社製ディジタル・オーディオ・プロセッサ「YSS950」やD-Aコンバータ,アンプ,無指向性マイクなどで実現されている.YSS950は32ビット浮動小数点DSPや16チャネルの入出力回路,補正動作に必要なメモリなどを内蔵している.

A-DコンバータやD-Aコンバータを搭載したYSS950の評価ボードには,ユーザ側でパラメータを設定するためのファームウェアも付属する.

[写真4] 自動音場補正システムの説明パネル

車内の前後左右,センタなどに搭載されている最大7.1チャネルのスピーカの音を,特定の位置に座る人に最適な特性となるように補正する

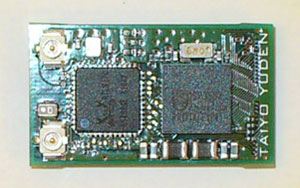

●Wireless USB1.0,WiMedia MAC1.0に準拠したコントローラIC

フィリップス エレクトロニクス ジャパンは,Certified Wireless USB1.0規格とWiMedia MAC1.0規格に準拠したコントローラIC「ISP3582」についてのデモンストレーションを行った.本ICは,アンテナに接続されている物理層ドライバICへのインターフェースと,組み込みボードに搭載されているCPUなどへのインターフェースを備えている.対応するデータ転送速度は480Mbps.また,本ICの汎用I/OはDMA(direct memory access controller)機能を搭載している.これにより,CPUだけでなく,ASICやASSPなどとも直接接続できる.

同社のブースでは,本ICのほか,台湾Realtek Semiconductor社のUWB物理層ドライバ「RTL8170」や十数点のチップCR,水晶発振子2個,コネクタなどを搭載した小型モジュールが展示されていた(写真5).外形寸法は14.4mm×25mmと小さい.本モジュールの製造は太陽誘電が担当した.2007年に量産出荷を開始する予定.

[写真5] Certified Wireless USB1.0規格とWiMedia MAC1.0規格に準拠したコントローラ・モジュール

ISP3582のほか,台湾Realtek Semiconductor社のUWB物理層ドライバ「RTL8170」や十数点のチップCR,水晶発振子2個,コネクタなどを搭載する

●情報端末や操作パネルの制御用ARMマイコン

アプローズテクノロジーズは,情報端末や操作パネルのユーザ・インターフェース制御などに利用できるARMマイコン「AP4010」のデモンストレーションを行った.本マイコンを搭載したPOS(point of sale)端末とタッチ・パネル・ゲームを展示した(写真6).

AP4010は,CPUコアとしてARM926EJ-Sを搭載する.αブレンディングやアファイン変換などの2次元グラフィックス・アクセラレータや,最大SVGA(800×600ピクセル)に対応したLCDコントローラ,USBインターフェース,メモリ・コントローラ,UART,GPIO,PS/2インターフェース,オーディオ用A-D/D-Aコンバータなどを内蔵している.現在,サンプル出荷中.2006年10月から量産出荷を開始する予定.

[写真6] ARMマイコンによるPOS端末とタッチパネル・ゲームのデモンストレーション

ARM926EJ-Sコアを搭載したマイクロコントローラ(AP4010)のデモンストレーション.右端の「知育玩具 ビーナ(セガトイズ製)」には,ARM7TDMIコアを搭載した同社のARMマイコン「AP2010」が組み込まれている

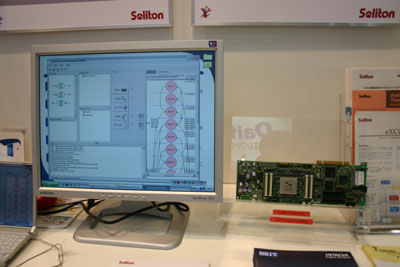

●FPGA専用のANSI C入力ビヘイビア合成ツール

ソリトンシステムズは,米国Y Explorations社(YXI)が開発したANSI C入力のビヘイビア合成ツールのFPGA専用版「eXCite FPGA」を展示した(写真7).FPGA開発,およびFPGAを利用したASIC向けのプロトタイプの開発に利用できる.ターゲット・デバイスを米国Altera社と米国Xilinx社のFPGA,および米国Actel社の「ProASIC3ファミリ」に絞った(ASIC用のライブラリは使用できない).また,対応するOSはWindows 2000/XP,ライセンス形態はノード・ロックのみである.機能をFPGA設計に求められるものに絞って,価格(ライセンス料金)を抑えたという.

本ツールは,ビヘイビア合成ツールの基本機能であるスケジューリング機能のほか,パイプライン合成やビット幅最適化,テストベンチの自動生成,インターフェース合成などの機能を備えている.出力は,VHDLまたはVerilog HDLのRTL(register transfer level)記述である.

[写真7] FPGA専用ビヘイビア合成ツールの展示

左がeXCite FPGAの実行画面.価格は200万円から.右は日立インフォメーションテクノロジーのプロトタイプ検証用FPGAボード「LogicBench」

NECグループのブースでは,JAXA(宇宙航空研究開発機構)が中心となって開発したシステム・レベル設計環境「ELEGANT」の紹介が行われていた.ELEGANTは,LSIの仕様モデルをアーキテクチャ・モデルやネットワーク・モデルからバス・トランザクション・モデル,通信モデル,サイクル精度モデルへと詳細化していく作業を支援することを目的とした設計環境である.複数の国産ツールと米国の大学が開発したツールを統合して構成した.シミュレーション・サブシステムにはインターデザイン・テクノロジーの「VisualSpec」が,設計詳細化サブシステムには米国University of California, Irvineの「SER(Specify-Explore-Refine)」が,ビヘイビア合成サブシステムにはNECの「Cyber」が,構成管理ツールには富士通の「ENABLER」が,形式的検証サブシステムには富士通の等価性検証ツールとデッドロック検証ツール,データ競合検証ツールが採用されている.

この設計環境を利用して,人工衛星の姿勢制御ソフトウェアのシミュレーションを試行したという.また,人工衛星内ネットワーク用インターフェース(SpaceWire)のハードウェア・ソフトウェア分割やビヘイビア合成ツールによるRTLモデル(FPGA実装用)の作成なども行った.