松下がディジタル家電用プラットホームの成果物を展示 ――CEATEC JAPAN 2005

日本を代表するエレクトロニクス製品・技術の展示会CEATEC JAPAN 2005が日本コンベンションセンター(幕張メッセ,千葉県千葉市)で2005年10月4~8日に開催された(写真1).来場者数は199,680名.前年の来場者数182,490名を上回った.

CEATECは,映像機器や通信機器,半導体,一般電子部品,ディスプレイ,製造装置など,対象分野が非常に広い.本レポートでは半導体を中心に,来場者の注目を集めていた出展物を紹介する.例えば今回のCEATECでは,松下電器産業やNECエレクトロニクスなどがディジタル家電の開発用統合プラットホームに関する展示を行い,来場者の注目を集めていた.

[写真1] CEATEC JAPANの会場風景

半導体ゾーンにて.2005年10月5日に撮影.

●ディジタル家電のソフトウェア開発環境を構築

ディジタル家電の機能向上により,ソフトウェア開発の負担は増大する一方である.そこで,家電メーカや半導体メーカはソフトウェアを共有し,開発負担を軽減するしくみの構築に取り組んでいる.

例えば松下電器産業は,ディジタル家電の開発用統合プラットホーム「UniPhier(ユニフィエ)」を利用して開発した電子機器の事例を紹介した.UniPhierは,ソフトウェア(ミドルウェアやOS,デバイス・ドライバなど)とハードウェア(マルチプロセッサ・コアを内蔵したシステムLSI)を共通化することによって,機器開発の負担を軽減するしくみである(写真2).用途に応じて,「携帯電話用UniPhier」,「ホームAV/カーAV用UniPhier」,「パーソナルAV用UniPhier」の3種類の基本構成が用意されている.

同社の展示ブースでは,「携帯電話用UniPhier」の応用事例として携帯電話機「FOMA P901iTV」(写真3)を,「カーAV用UniPhier」の応用事例として車載用ナビゲーション装置「NHDN-W55G」(写真4)を,「パーソナルAV用UniPhier」の応用事例としてビデオカメラ「SDR-S100」(写真5)をそれぞれ展示していた.

[写真2] ディジタル家電開発用統合プラットホーム「UniPhier」 (写真をクリックすると拡大)

松下電器産業の展示.

(b) 「携帯電話用UniPhier」を利用して開発した携帯電話機

[写真3] 「携帯電話用UniPhier」の応用事例

(a)はシステム構成.地上ディジタル・テレビの1セグメント放送を受信できる.(b)は開発事例である携帯電話機「FOMA P901iTV」.松下電器産業の展示.

(b) 「カーAV用UniPhier」を利用して開発したナビゲーション・システム

[写真4] 「カーAV用UniPhier」の応用事例

2次元/3次元グラフィックス処理LSIの開発に適用した.(a)はLSIの内部構成.(b)は開発事例である車載用ナビゲーション装置「NHDN-W55G」.松下電器産業の展示.

[写真5] 「パーソナルAV用UniPhier」の展示

動画像圧縮伸張規格であるMPEG-2による映像の記録再生を実演してみせた.このほか,開発事例であるビデオ・カメラ「SDR-S100」を展示した.松下電器産業の展示.

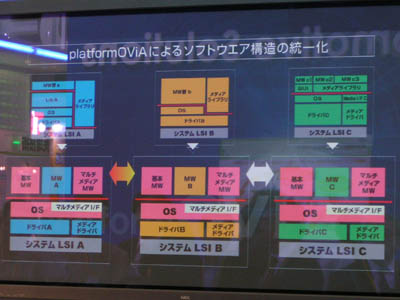

一方,NECエレクトロニクスは,ディジタル家電の開発用統合プラットホーム「platformOViA」を展示した.マルチメディア関連のインターフェースを組み込んだOSをミドルウェアに対する共通のインターフェースとし,ソフトウェア開発を容易化している(写真6).携帯電話機やディジタル・カメラ,車載システムなどでミドルウェアを共有できるようになる.ハードウェアであるシステムLSIは,用途別にいくつかの構成を用意する.なお,platformOViAに対応するOSは現在のところ,米国MontaVista Software社の「MontaVista Linux」だけである.

[写真6] ディジタル家電の開発用統合プラットホーム「platformOViA」

NECエレクトロニクスの展示.

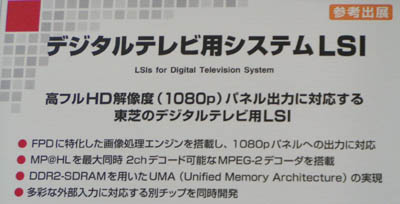

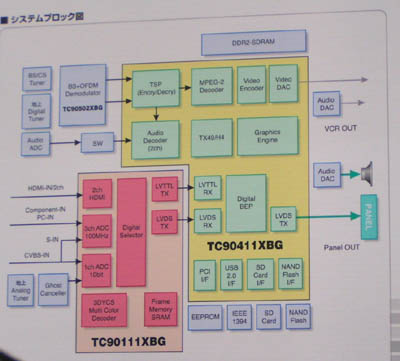

●1080pディジタル・ハイビジョン対応のテレビ用チップセット

ディジタル・テレビ放送受像機用半導体では,東芝がフルスペック・ハイビジョン(1080p)対応の薄型テレビ向けチップセットを展示した(写真7).本チップセットは,おもにディジタル信号処理を担う「TC90411XBG」と,おもにアナログ・ディジタル変換を担う「TC90111XBG」の2チップで構成される.東芝のフルスペック・ハイビジョン対応液晶テレビ受像機に採用された.

「TC90411XBG」は日本国内の地上ディジタル放送,国内のBSディジタル放送,110度CSディジタル放送,米国地上ディジタル放送に対応する.2チャネルのMPEG-2のMP@ML(Main Profile at Main Level)を同時に復号できる.「TC90111XBG」はアナログ・コンポジット信号,アナログ・コンポーネント信号,Sビデオ信号などに対応する.

[写真7] 1080pディジタル・ハイビジョン対応の薄型テレビ向けチップセット

東芝の展示.

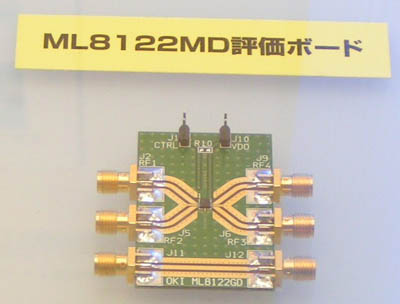

高周波デバイスでは,沖電気工業がSOS(silicon on sapphire)技術によるCMOS RFスイッチLSI「ML8122MD」を出品した(写真8). CMOS技術による静電気保護回路を組み込んだことで,ガリウム・ヒ素(GaAs)技術によるRFスイッチLSIと比べて静電気放電に対する耐性を高めた.製造コストはGaAsのスイッチとほぼ同じという.スイッチの種別はDPDT(double pole double throw).

[写真8] SOS(silicon on sapphire)技術によるCMOS RFスイッチLSI

ML8122MDは移動体無線端末のアンテナ・スイッチに用いられる.(a)は評価ボード.(b)は説明用パネル.(c)はサファイアの実物.沖電気工業の展示.

●デバイス,回路,設計の組み合わせで消費電力を低減

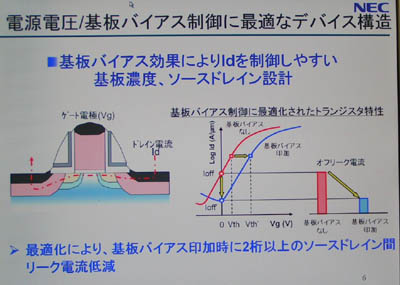

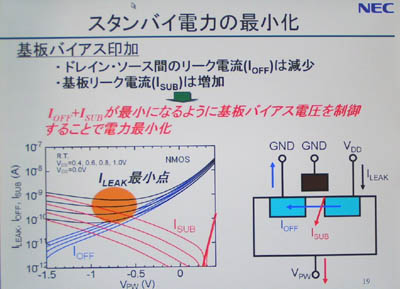

半導体技術では,NECエレクトロニクスが65nm世代のLSIに向けた低消費電力化技術を,液晶モニタのスライド・ショーとして紹介していた(写真9).この技術を用いることで待機時の消費電力を低減する.携帯電話機の待ち受け時間を従来の30倍に延ばすという.

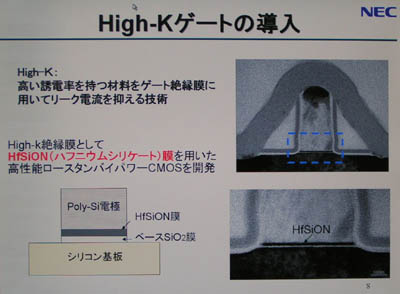

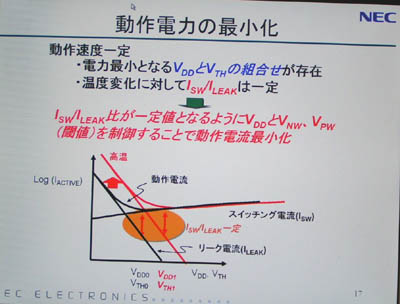

デバイス技術と回路技術,設計技術の組み合わせによって実現する.デバイス技術では基板バイアスによってオフリーク電流を抑えるとともに,高誘電率材料をゲート絶縁膜に使ってゲート・リーク電流を低減する.回路技術では,「スイッチング電流/リーク電流」の値が一定になるように電源電圧としきい電圧を制御し,動作時の消費電力を最小にする.また「ドレイン・ソース間リーク電流と基板リーク電流」の合計値が最小になるように基板バイアス電圧を制御し,待機時の消費電力を最小にする.設計技術では,LSI設計者に意識させることなく,基板バイアスの制御回路を自動的に組み込むとともに,LSIの回路ブロックごとに基板バイアスを独立に制御できるようにする.

</span>

</span>

(e) 待機時電流の低減に関するスライド

[写真9] 65nm世代のLSIに向けた低消費電力化技術

液晶モニタにスライド・ショー形式で展示していた.デバイス技術では基板バイアスによってトランジスタのオフリーク電流を抑え(写真(b)),高誘電率(high-k)材料をゲート絶縁膜に使ってゲート・リーク電流を低減する(写真(c)).回路技術では,「スイッチング電流/リーク電流」の値が一定になるように電源電圧としきい電圧を制御し,動作時の消費電力を最小化する(写真(d)).また,「ドレイン・ソース間リーク電流と基板リーク電流」の合計値が最小になるように,基板バイアス電圧を制御し,待機時の消費電力を最小限に抑える(写真(e)).NECエレクトロニクスの展示.

また東芝は,45nm世代の製造プロセスに関するパネル展示を行っていた.現在の最先端世代である90nm世代と比べ,LSIのトランジスタ数は4倍,動作周波数は2倍,消費電力(機能当たり)は1/4になる.45nm世代の製造には液浸露光技術,低リークのゲート絶縁膜,極浅接合技術,ポーラスな低誘電率層間絶縁膜,高誘電率DRAMセル・キャパシタなどの要素技術が使われるという.

ふくだ・あきら

テクニカルライター/アナリスト

http://d.hatena.ne.jp/affiliate_with/