開発工程の最上流"ESL"と最下流"DFM"を巻き込んでLSI設計工程を最適化 ――42nd Design Automation Conference(DAC)

2005年6月13日~17日,米国カリフォルニア州Anaheimにて,LSIの設計自動化(EDA:electronic design automation)に関する国際学会/展示会「42nd Design Automation Conference(DAC)」が開催された(写真1).今年のDACでは,RTL(register transfer level)設計より前の工程(いわゆるビヘイビア・レベルやシステム・レベル)を支援するESL(electronic system level)ツールや,LSIの歩留まりを左右する製造容易化設計(DFM:design for manufacturability)といったキーワードに関連する発表や展示が相次いだ.すなわち,現在の開発の最上流(システム・レベル設計)と最下流(製造)を巻き込んだLSI設計工程の最適化に話題が集中していた.また,LSIやパッケージ,プリント基板を包括的に取り扱える解析ツールも続々登場した.

[写真1] Anaheim Convention Center ※写真をクリックすると拡大します

2005年6月13~17日に,42nd Design Automation Conferenceが開催された.

●トランザクション・レベルを三つの視点に分けてサポート

SystemCに関する標準化・普及推進団体である米国Open SystemC Initiative(OSCI)は,SystemC 2.1の言語仕様を定義したLRM(language reference manual)を米国IEEE(The Institute of Electrical and Electronics Engineers, Inc.)に正式に提供したことを発表した.これに基づいてIEEEのP1666ワーキング・グループがSystemCの承認投票などを進めており,年内には標準化作業が完了する予定である.こうした動きを受けて,今回のDACでは多くのEDAベンダがSystemC 2.1の正式サポートを表明した.

例えば米国CoWare社は,同社のシステム・レベル設計ツール「ConvergenSC」がSystemC 2.1の言語仕様に対応したことを発表した.また,OSCIがまとめたTLM(transaction level modeling)手法にのっとったサンプル記述やライブラリを用意したことも明らかにした.

同社では,トランザクション・レベルをプログラマ視点(PV:programmer's view),アーキテクト視点(AV:architect's view),検証視点(VV:verification view)の3階層に分けて考えている.プログラマ視点は,おもに組み込みソフトウェア開発者が思い浮かべる設計抽象度である.すなわちCPUが命令セット・シミュレータとしてモデル化され,その上でソフトウェアのオブジェクト・コードが実行され,さらにCPUはバスを介して機能モジュールやDMAと接続される.一方,アーキテクト視点はネットワークやバス,およびバス間をつなぐバス・ブリッジによって各種モジュール(メモリ,およびデータを送り出すプロデューサなど)が接続される設計抽象度である.この抽象度ではクロックの概念はない.三つ目の検証視点は,アーキテクト視点に対してサイクル精度のタイミング情報を付け加えた抽象度である.

同社では,これらの各視点に対応したプロトコルやトランザクタ,チャネル,ブリッジなどのサンプル・モデル,およびコーディング・ガイドラインを提供していく方針.検証視点についてはすでに現在のバージョンでサポートしている.今年(2005年)の第4四半期に出荷を予定しているバージョン2005.2ではアーキテクト視点の,その次のバージョンではプログラマ視点のサポートを開始するという.

また,米国Forte Design Systems社も,同社のビヘイビア合成ツール「Cynthesizer」がSystemC 2.1に対応したと発表した.最新版のCynthesizerは「Modular IP Synthesis」と呼ぶ機能を備えており,モジュール間の通信チャネルの実装方式をユーザが自由に選択できるようになっているという.例えば,異なるプロトコルの通信チャネルに置き換えることができるという.

●シミュレータはSystemCとSystemVerilogの両対応に

最近のHDLシミュレータの多くはVerilog HDLとVHDLの両方に対応しており,内部に複数の言語を取り扱うためのしくみを備えているケースが多い.そのためもあってか,シミュレータ・ベンダの大半は,SystemCとSystemVerilogの両方への対応を表明している.

例えば米国Mentor Graphics社は,同社が2005年5月に発表したSystemVerilog,Verilog HDL,VHDL,PSL,SystemCの5言語に対応したシミュレータ「Questa」のデモンストレーションを行った.Questa製品として,同社はSystemVerilogとVerilog HDL(Verilog 2001)に対応した「Questa SystemVerilog」と,SystemVerilog,Verilog HDL,VHDL,PSL,SystemCに対応した「Questa AFV」の2種類を出荷している.いずれも機能検証手法であるアサーションや制約付きランダム・テスト生成,機能カバレッジに必要な機能を標準装備しているという.

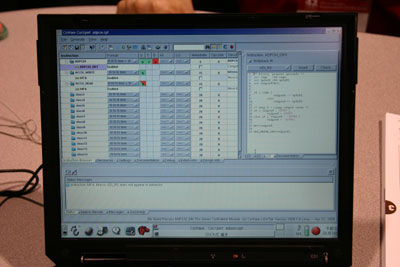

また,米国Aldec社も,同社のHDLシミュレータ製品においてSystemCとSystemVerilogの両方をサポートすることを表明している(写真2).主にFPGAの検証などをねらったHDLシミュレータ「Active-HDL」では,同一カーネル上でVHDL,Verilog HDL,SystemCを取り扱えるようにする.一方,主にASICの検証などに使われるHDLシミュレータ「Riviera」はSystemVerilog 3.1a(SystemVerilogアサーションを含む)に対応する.Rivieraについては,処理速度を引き上げられるように米国AMD(Advanced Micro Devices)社のマイクロプロセッサ「Opteron」などの上で稼働する64ビットLinux OSもサポートする.

[写真2] Active-HDLのデモンストレーションのようす

FPGAの検証などをねらったAldec社の統合型HDLシミュレータ.SystemCモデルを同一カーネル上で検証できるようにするという.本ツールはグラフィカル入力機能も備えている.

●形式的検証ツールやデバッガもSystemC対応へ

米国Calypto Design Systems社は形式的検証技術を利用した等価性検証ツール「SLEC」を展示した(写真3).SLECには,Verilog HDL/VHDLのRTL記述(順序回路)どうしの論理的等価性をチェックする「SLEC RTL」と,SystemCのビヘイビア記述とVerilog HDL/VHDLのRTL記述の論理的等価性をチェックする「SLEC SYSTEM」の2種類がある.例えば,処理時間を短くするために,乗算器などをビット単位ではなくワード単位で比較する手法や,回路動作中に実際に使われる状態か使われない状態かを判定し,それらの状態遷移を逆方向にトレースして検証が必要かどうかを確認する手法などを採用しているという.

同社はSLECについて,Mentor Graphics社と提携を結んだことも発表した.Mentor社のC/C++入力のビヘイビア合成ツール「Catapult C Synthesis」と組み合わせて使えるようにした.例えば,ビヘイビア合成の過程で行った操作に伴う情報(ビヘイビア記述の信号とRTL回路の信号の間の等価点情報やスケジューリング情報など)をSLECに渡して処理時間を短縮できるようにした.

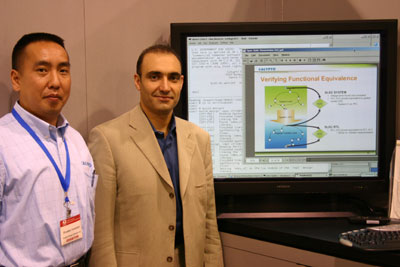

[写真3] SLECのプレゼンテーションのようす

左側は,Calypto社 Senior Field Application Engineerの山本修作氏とVice President, Marketing & Business DevelopmentのMichael Sanie氏.

また,米国Novas Software社は,トランザクション・レベルの解析やSystemC記述のトレースを行えるデバッガ「nESL」のデモンストレーションを行った(写真4).信号波形をトランザクションの形で表示したり,スプレッド・シートやグラフを利用してバス使用率やメモリ使用率,トランザクション数などを出力できる.

今回のDACでは,Novas社をはじめとする6社のデバッガ・ベンダやJTAGツール・ベンダが,「DFD(Design-for-Debug)Consortium」という団体を設立したと発表した.LSI設計や量産テスト,シリコン・デバッグの各工程間のテスト・データの受け渡しやツール間連携を円滑にすることを目指す.例えば,これらの工程で利用されるデータ・フォーマットの標準化などに取り組んでいくという.Novas社のほか,米国Corelis社,米国DAFCA社,米国First Silicon Solutions(FS2)社,米国Intellitech社,オランダJTAG Technologies社が本団体への参加を表明している.

[写真4] Novas Software社のブースのようす

Novas社のデバッグ・ツール「Verdi」のデモンストレーションが行われていた.

●RTL記述からC++/SystemCモデルを生成

米国TenisonEDA社は,RTLのHDLモデルからサイクル精度のC++モデルやSystemCモデル(C++モデルに接続するラッパ)を生成するツール「VTOC」のデモンストレーションを行った(写真5).RTLモデルの代わりにサイクル精度のモデルを利用することで,シミュレーション速度が10~100倍速くなるという.このC++モデルは,PLI(programming language interface)を介してVerilog HDLシミュレータに接続することも可能.

また,同社は,C++モデルをコンパイルしてオブジェクト・コードに変換し,詳細情報を隠ぺいするツール「VTOC Export」も発表した.例えば,VTOCで生成したC++モデルをIPコアとして流通させる場合などに役に立つという.ライセンスの管理にはFLEXlmを利用できる.将来,同社はさらに抽象度の高いトランザクション・レベル(プログラマ視点)などのモデルも生成できるようにするという.

[写真5] VTOCのデモンストレーションのようす

RTLのHDLモデルからサイクル精度のC++モデルやSystemCモデルを生成する.RTLのHDLモデルを利用した場合よりも,シミュレーション時間を短縮することができる.

●NECが高位設計の統合環境と実績を米国でアピール

今回のDACには,NEC情報システムズが出展していた.同社は,NECが開発したビヘイビア合成ツールや形式的検証ツールを含むシステムLSI設計用のツール群「CyberWorkBench」のデモンストレーションを行った(写真6).NECのビヘイビア合成ツール「Cyber」は,実際に多くのLSI開発プロジェクトに適用されており,最近では同社製のダイナミック・リコンフィギャラブル・プロセッサのコンフィグレーション・データの開発環境としても利用されている.ただし,現段階ではまだ外販の予定は決まっておらず,同社にASICを発注している特定の顧客にのみ貸し出しているという.

CyberWorkBenchを構成するツールの中で,今回,初めて公開されたのは,C言語入力の形式的検証ツール群である.C言語で記述した仕様(プロパティ)と矛盾しないかどうかをチェックするプロパティ検証ツールと,C言語のビヘイビア記述とVerilog HDL/VHDLのRTL記述の間の論理的等価性をチェックする等価性検証ツールを発表した.プロパティ検証ツールについては,Cyberがビヘイビア合成の過程で行った操作に伴う情報(等価点情報など)を利用することにより,処理時間を短縮しているという.このほか,ビヘイビア合成ツールと連携して利用できるフロアプランナやテストベンチ生成ツール,CPUバス・インターフェース生成ツール,ダイナミック・リコンフィギャラブル・プロセッサ用のオンチップ・デバッガなども初めて公開した.

[写真6] NEC情報システムズのブースのようす

CyberWorkBenchのデモンストレーションが行われた.このほか,LSIパッケージの設計支援ツールなども展示されていた.

●コプロセッサのハードとソフトを自動生成

米国CriticalBlue社は,コプロセッサ合成ツール「Cascade」のデモンストレーションを行った(写真7).例えば,画像処理や音声処理,データ圧縮/伸張,暗号化,エラー訂正などを高速化するコプロセッサを生成できるという.メインCPUとして,現在はARMv4命令セット・アーキテクチャを実装したプロセッサに対応している.

ユーザは英国ARM社などのソフトウェア開発環境を利用してソフトウェアをコンパイル・実行し,プロファイルをとる.その結果をもとに,コプロセッサに実行させたい処理を元のソフトウェアから切り出す.この情報を元に,コプロセッサのRTLコード(Verilog HDL,VHDL),テストベンチ,合成スクリプト,およびコプロセッサのマイクロコードを生成する.また,性能解析用にサイクル精度のCモデルも生成する.

本コプロセッサは,命令キャッシュやデータ・キャッシュ,キャッシュ制御回路,実行制御回路,システム・バス・インターフェース(AMBA AHB)を搭載している.また,DMAコントローラを利用することにより,メインCPUとコプロセッサを並行動作させることもできる.

[写真7] Cascadeのデモンストレーションのようす

Cascadeによって生成したコプロセッサを使って動画像の圧縮/伸張処理を行っている.

また,CoWare社は,同社のプロセッサ合成ツール「LISATek」がMIPS 24Kプロセッサ・コアの命令拡張機能である「CoreExtend」に対応したことを明らかにした(写真8).すなわち,MIPS 24Kプロセッサ・コアにカスタム命令を追加する場合,本ツールを利用して開発できるようになった.カスタム・プロセッサを開発するためのプロセッサ合成ツールが,標準的な命令セット・アーキテクチャを備えるCPUのカスタマイズに利用できる例は珍しい.

[写真8] CORXpertの画面例

MIPS 24Kプロセッサ・コアに対応した「CORXpert for the 24K Pro Seriesscore」のデモンストレーションが行われていた.

●プロトコルをグラフィカルに設計・検証

米国Bellum Software社はプロトコル設計ツール「ProtoCollum」を発表した(写真9).システムLSI上のオンチップ・バスやオンチップ・ネットワークを設計するシステム・アーキテクトが利用することを想定している.

ユーザは,グラフィカルな画面を利用し,対話的にトランザクション・レベル(クロック・サイクルなし)の通信プロトコルを入力する.具体的には,各ノード(プロセッサなど)における通信処理の手順を時系列に沿って記述する.テスト・シナリオもグラフィカルな画面を使って入力できる.作成した通信プロトコルとテスト・シナリオを組み合わせてシミュレーションし,不ぐあいを検出する.作成した通信プロトコルから,実行可能なCモデルなどを生成する.このモデルは,RTL検証用のテストベンチとして利用できる.

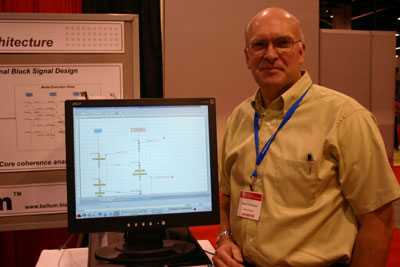

[写真9] ProtoCollumのデモンストレーションのようす

右側は,Bellum社 Founder and Chief Technical OfficerのReed Christensen氏.同氏は,米国Intel社でP6プロセッサ・コアのアーキテクチャ検証の業務に携わっていた.

●大規模回路を扱えるプロパティ検証ツールがPSL 1.1に対応

米国Jasper Design Automation社は,同社のプロパティ検証ツール「JasperGold」の廉価版にあたる「JasperGold Express」を2005年第3四半期に出荷すると発表した(写真10).JasperGoldは比較的規模の大きい回路(状態数の多い回路)を取り扱えるプロパティ検証ツールで,バグの原因となる箇所を特定する「Precognitive Engine」と呼ばれる機能を備えている.JasperGold Expressではこの機能を省略して価格を下げた.多くの設計エンジニアにとってはバグを検出する機能が重要で,バグの原因を特定する機能を必要とするユーザの数は限られると同社では見ている.

[写真10] JasperGoldのデモンストレーションのようす

Jasper社のプロパティ検証ツールは,比較的大規模な回路を扱える点が特徴である.今回,機能を抑えた廉価版のツールを発表した.

●歩留まり向上のため,ファウンドリは製造容易化設計に注力

台湾TSMC(Taiwan Semiconductor Manufacturing Co.)は,65nmプロセス向けの設計フロー「Reference Flow 6.0」を発表した.おもに消費電力管理と製造容易化設計に関する機能を強化した.

消費電力については,電圧スケーリングによって電源電圧を引き下げる領域(voltage island)を複数設けられるようにした.また,しきい値電圧の異なるトランジスタを集積するMTCMOS(multi-threshold complementary metal oxide semiconductor)について,待機時の電源電圧を細かく制御できるようにした.また,これらの回路構成に対応したネットリスト生成やフロアプラン,信号解析などのツールを用意した.

製造容易化設計については,歩留まりを改善するため,ダミー・メタルを挿入したり,配線幅を細かく調整できるようにした.このほか,同社の顧客向けに製造容易化設計を支援するサービスも開始した.製造容易化設計のためのガイドラインやルール・チェッカを顧客に提供する.例えば,OPC(optical proximity correction;光近接効果補正)ツールの処理時間が短くなるような設計ルールを定義した.さらに,設計変更が歩留まりにどのような影響を与えるかを解析するサービスや,リソグラフィ工程をチェックするサービス,LSIパッケージのシミュレーション・モデルを開発するサービス,スキャン・テストによる故障診断を行うサービスなども実施する.

●LSIからプリント基板までシームレスに扱う解析ツールが続々

米国Sigrity社は,LSIパッケージの影響も含めてLSIの電源ネットワークの電圧変動(グラウンド・バウンス)を解析できるツール「CoDesign Studio」を展示した(写真11).従来,電源ネットワークの解析ではLSIパッケージの影響を無視し,LSI内部のみをモデル化して解析することが多かった.しかし,最近ではディジタルLSIの動作周波数が上がり,LSIパッケージのピンやボンディング・ワイヤなどの電気的影響を無視できなくなってきている.また,電源電圧が低下してノイズ・マージンも減っている.そのため,LSIパッケージを含めた精度の高い電源ネットワーク解析が求められている.

本ツールは,同社のLSI用の電源ネットワーク解析ツールである「XcitePI」と,ボード/LSIパッケージ用のノイズ解析ツール「SPEED2000」を統合したものである.回路シミュレータ,伝送線路シミュレータ,電磁界シミュレータの3種類の解析ツールを内蔵しており,要求される精度や取り扱うモデルの複雑さに応じて,解析手法が自動的に選択される.LSIパッケージについては,米国Cadence Design Systems社の「APD」や米国Synopsys社の「Encore」といったLSIパッケージ設計ツールで作成したレイアウト・データなどを読み込める.

[写真11] CoDesign Studioのデモンストレーションのようす

Sigrity社のLSI用の電源ネットワーク解析ツールである「XcitePI」と,ボード/パッケージ用のノイズ解析ツール「SPEED2000」が統合された.

また,米国Optimal社は,LSIやLSIパッケージ,プリント基板の信号ネットワークと電源ネットワークを同時に解析できるツールを発表した.信号ネットワークの同時スイッチングなどを解析するツール「O-Wave」と,電源ネットワークのIRドロップやグラウンド・バウンスを解析するツール「PowerGrid」を組み合わせた(写真12).いずれも有限要素法を用いる電磁界シミュレータ(フィールド・ソルバ)を備えている.例えば,隣接する複数のネットの相互作用も解析できるという.

一般に,電磁界シミュレータを用いる手法では,解析精度は向上するが,処理に多くの時間がかかるケースが多い.そのため,従来はモデルを簡素化するか,あるいは回路を分割し,それぞれの回路に対して個別に解析するという方法が採られてきた(例えば前述のSigrity社の手法は後者).しかし,前者の手法では精度が低下するという問題が,後者の手法では回路全体で見たときの精度がどの程度になるのか判断できないという問題がある.本ツールでは,多重格子法などのアルゴリズムを用いて処理時間やメモリ使用量を削減することにより,こうした問題を回避しているという.

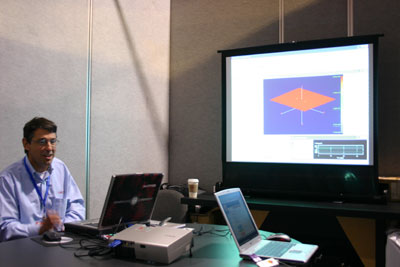

[写真12] O-Waveのプレゼンテーションのようす

右側は,Optimal社 Chief Technical OfficerのAn-Yu Kuo氏.

このほか,米国AWR(Applied Wave Research)社も,LSIやLSIパッケージ,プリント基板を同時に取り扱える高周波回路解析ツール「AWR SI 2005」のデモンストレーションを行った(写真13).本ツールは,高周波回路シミュレータや電磁界シミュレータなどを搭載している.LSIやLSIパッケージ,プリント基板のモデルを単一のデータ・フォーマットで記述でき,レイアウト・データを含めて時間領域や周波数領域で解析できるという.

[写真13] AWR SI 2005のデモンストレーションのようす

右側は,AWR社 President and CEOのJames Spoto氏.