入出力ピン当たりのデータ転送速度が8Gbpsの次世代高速メモリ技術を開発中 ――ラムバス デベロッパ フォーラム JAPAN 2005

半導体用高速インターフェース技術の開発企業である米国Rambus社は,2005年7月7日~8日に東京・渋谷のセルリアンタワー東急ホテルで,回路設計者向けセミナ「ラムバス デベロッパ フォーラム JAPAN 2005」を開催した.高速メモリ・インターフェース技術である「XDR(Extreme Data Rate)」や「DDR(double data rate)」,高速入出力インターフェース技術である「PCI Express(Peripheral Component Interconnect Express)」などの内容が詳しく紹介された.

●2007年にはXDR2対応半導体製品が登場

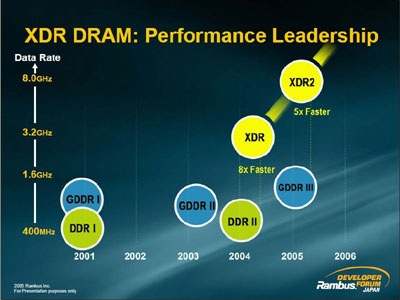

Rambus社は,毎年,7月上旬に東京で回路設計者向けセミナを開催し,最新の技術動向を紹介している.今年は,高速メモリ・インターフェース技術XDRの次世代版である「XDR2」を開発中であることを公表した(写真1).2007年には,XDR2技術を組み込んだ半導体製品を出荷できるようになるという.

[写真1] 各種の高速メモリ・インターフェース技術 ※写真をクリックすると拡大します

入出力ピン当たりのデータ転送速度が8Gbpsときわめて高いインターフェース技術「XDR2」を開発中であることを公表した.

XDR2技術によるデータ転送速度は,入出力ピン当たり8Gbpsときわめて高い.×16ビット構成のDRAMにXDR2技術を導入すれば,16Gバイト/sものデータ転送を実現できることになる.

Rambus社が開発した現行のXDRインターフェースは,主に,以下の三つの要素技術で構成される.

- システム・クロックの8倍の周波数でデータを転送する技術(ODR:Octal Data Rate)

- 約200mVと小さな振幅でデータを伝送する差動伝送技術(DRSL:Differential Rambus Signaling Levels)

- DRAMとメモリ・コントローラの間の遅延時間を2.5ps単位で制御する技術(FlexPhase)

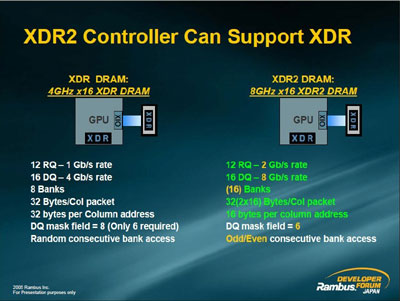

これに対してXDR2インターフェースでは,システム・クロックの16倍の周波数でデータを転送する.システム・クロックが500MHzのとき,XDRインターフェースではデータ転送周波数が4GHzになるのに対し,XDR2インターフェースでは8GHzと,XDRの2倍に増える(写真2).

[写真2] XDRインターフェースとXDR2インターフェースの違い

システム・クロック周波数が500MHzの場合を比較した.データ転送周波数はXDRインターフェースが4GHz,XDR2インターフェースが8GHzとなる.また,XDR2のメモリ・コントローラはXDRに対して上位互換を維持する.

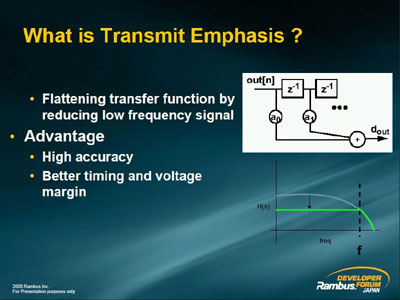

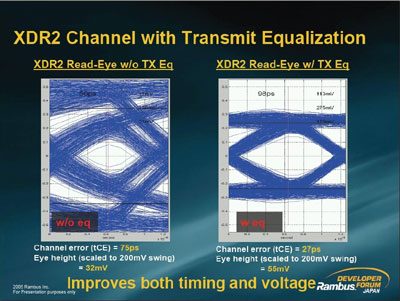

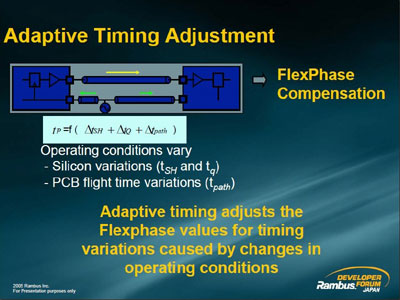

また,信号のひずみを少なくする出力回路を搭載する.Rambus社は「トランスミット・イコライゼーション(Transmit Equalization)」と呼んでいる.出力信号の低周波側の利得を意図的に抑えることによって,高周波側の信号ひずみを抑える(写真3).さらに,動作中にメモリとコントローラの間の遅延時間が変化したときにタイミングを補正する技術「アダプティブ・タイミング(Adaptive Timing)」を組み込む.XDRインターフェースでは,動作前に遅延時間を計測してタイミングを補正していた.これに対してXDR2では,電源電圧変動や温度変動などによって動作中に遅延時間が変化した場合でも,タイミングに補正をかける(写真4).

また,DRAMのコア部とインターフェース部でデータをやり取りする方式を変える.現行のXDR DRAMでは,コア部を8バンクに分け,二つのバンクから同時にデータをアクセスしていた.XDR2 DRAMでは8バンクの各バンクを奇数バンクと偶数バンクに分ける.そして二つの奇数バンクと二つの偶数バンクから交互にデータをアクセスする.列(コラム)アクセスの速度が高まるとともに,1回にアクセスするデータの単位が小さくなる.この方式を「マイクロスレッディング(Micro-threading)」とRambus社は呼んでいる.

[写真3] トランスミット・イコライゼーション(Transmit Equalization)

(a)のように信号の低周波成分の利得(図中では伝達関数)を下げ,高周波側の信号ひずみを減らす.この結果,信号ひずみの少ない(b)のようなアイ・パターンが得られる.

[写真4] アダプティブ・タイミング(Adaptive Timing)

メモリとコントローラ間の遅延時間を補正する技術「FlexPhase」を,動作中にも適用する.

●XDR DRAMモジュールを実際に動かす

現行のXDR技術を導入したDRAM(XDR DRAM)は,現在,東芝,エルピーダメモリ,韓国Samsung Electronics社の3社が製品を出荷中である(写真5).いずれも単体のDRAMであり,メイン・メモリを想定したモジュール製品はまだ登場していない.

[写真5] XDR DRAMの製品サンプル

左から東芝の512Mビット品,エルピーダメモリの512Mビット品,韓国Samsung Electronics社の512Mビット品.これらの3社はRambus社からXDR技術のライセンスを受けて,DRAMを開発・製品化している.Rambus社は技術開発企業であり,半導体製品は製造しない.

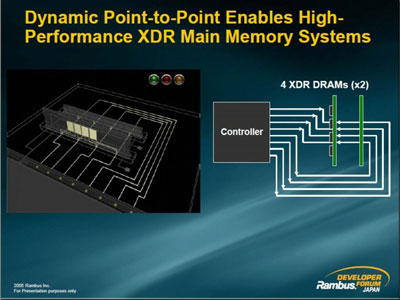

今回のフォーラムでは,XDR DRAMのメイン・メモリ用途を想定したモジュール技術をRambus社が公表した.一般的なシンクロナスDRAMモジュールと同じDIMMソケットに差し込む,カード型のモジュールである.搭載するモジュールの数は2個.メイン・ボードにはソケットをあらかじめ2個搭載しておく.1個のソケットにだけモジュールを載せるときは,空いたソケットにダミー基板(continuity module)を差し込む(写真6).

[写真6] XDR DRAMを主記憶に適用する

XDR DRAMモジュールを2個搭載できる主記憶の構成図.ソケットをあらかじめ2個装着しておく.1個のDRAMモジュールだけを搭載するときは,空いたソケットにダミー基板を差し込む必要がある.

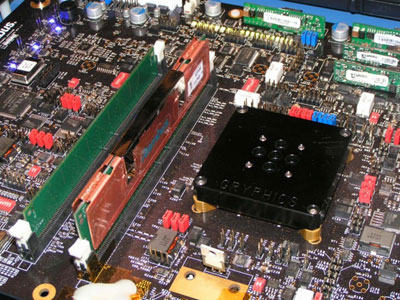

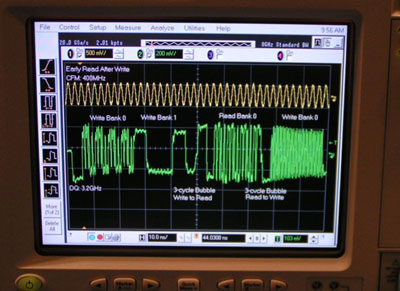

Rambus社の展示ブースでは,実際にモジュールを組み込んだボードを展示し,入出力ピン当たり3.2Gbpsのデータ転送を実行してみせていた(写真7,写真8).これは×36ビット構成のモジュールである(×4ビットはエラー訂正用コード).東芝の512MビットXDR DRAMを9個搭載する.DRAMの語構成は×4ビット.モジュール全体は銅(Cu)製のヒート・シンクで覆ってある.指でヒート・シンクを軽く触ってみると,かなり熱かった.

[写真7] XDR DRAMモジュールを搭載したボード

左側に2個のソケットがあり,モジュールを差し込めるようになっている.左側のソケットにはダミー基板が,右側のソケットにはXDR DRAMモジュールが装着されている.中央の黒い箱はXDRメモリ・コントローラを内蔵したASIC.

[写真8] XDR DRAMモジュールの動作波形

入出力ピン当たり3.2Gbpsの速度でデータを転送できている.

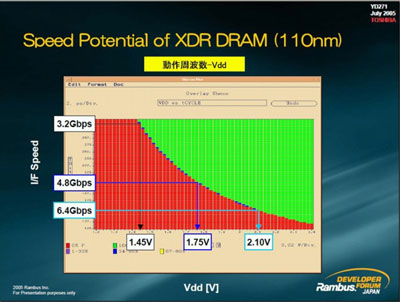

また,東芝は,XDR DRAMが入出力ピン当たり4.8Gbpsで動くことを示した(写真9).現在の製品仕様である3.2Gbpsは,電源電圧にかなり余裕があることがわかる.さらに仕様外だが電源電圧を2.1Vに上げ,6.4Gbpsと高い速度で動かしてみせた.

[写真9] XDR DRAMの電源電圧とデータ転送速度

緑色の領域が正常に動作したことを示す.規定の電源電圧である1.8Vのとき,4.8Gbpsで動かすことができた.電源電圧を2.1Vに上げると,6.4Gbpsで動作できることが示されている.

●PCI Expressシステムの開発支援用計測器が続々

このほか,展示ブースでは,PCI Expressバス・システムの開発を支援する計測器のデモンストレーションが目立っていた.

レクロイ・ジャパンは,16レーンのPCI Expressバスに対応したエキササイザ「PETrainer EML」とプロトコル・アナライザ「PETracer EML」を展示した.米国LeCroy社は2004年10月に,バス・アナライザ・メーカのCATC(Computer Access Technology Corporation)を買収している.これらはいずれも,旧CATCの製品である.

また,日本テクトロニクスは,PCI Expressバスのコンプライアンス・テストに対応したソフトウエア「TDSRT-Eye 2.0」をディジタル・ストレージ・オシロスコープ「TDS6154C」に組み込み,動作の実演を行った.「最近,コンプライアンス・テストの規格が一部変更された.そこで,規格変更に対応するソフトウェアを展示した」(展示ブースの説明員).

ふくだ・あきら

テクニカルライター/アナリスト

http://d.hatena.ne.jp/affiliate_with/