ASICベンダ各社がストラクチャードASIC製品を担いで存在感を誇示 ――Electronic Design and Solution (EDS) Fair 2005

2005年1月27日~28日,パシフィコ横浜(神奈川県横浜市)にて,設計自動化技術に関する展示会「Electronic Design and Solution (EDS) Fair 2005」が開催された(写真1).本展示会では,ここ数年,FPGA(field programmable gate array)に押され気味で元気のなかったASIC(application specific integrated circuit)ベンダが,ストラクチャードASICの新製品やユーザ事例などを発表して,存在感を誇示した.また,NECエレクトロニクス,米国LSI Logic社,富士通に続いて東芝も,ストラクチャードASICとよく似たコンセプトのマスタ・スライス型ASIC製品を発表した.

[写真1] Electronic Design and Solution Fair 2005の会場

パシフィコ横浜(神奈川県横浜市)にて開催された.

●ストラクチャードASICの新製品やユーザ事例が登場

LSI Logic社は,2004年1月中旬に発表した「RapidChip Integrator2ファミリ」についてのパネル展示を行った.本ストラクチャードASICは「Matrix-RAM」と呼ぶSRAMブロックを内蔵している.このSRAMブロックの内部には多数の小さな2ポートSRAMがマトリックス状に整列しており,ユーザの設計に合わせてこれが分割され,任意のメモリ・サイズやワード構成のSRAMとして使用される.任意のメモリ構成のSRAMに分割されるため,例えばFPGA向けに設計した回路を本ストラクチャードASICに実装する際に,FPGAの中のメモリ部分(分散メモリ,メモリ・ブロック)を直接Matrix-RAMにマッピングできるという.また,本ストラクチャードASICは,DDR(double data rate)2やDR(quad data rate)2,RLDRAM(Reduced Latency DRAM)II,FCRAM(Fast Cycle RAM)2y」などのメモリ・インターフェース規格に対応している.

NECエレクトロニクスは,同社のストラクチャードASIC「ISSP」のユーザ事例を公開した.同社のブースに,画像処理装置の設計会社であるアイ・シーが開発したハイビジョン放送用JPEG2000デコーダ・ボードを展示した(写真2).これは,JPEG2000フォーマットの圧縮データを,ハイビジョン・サイズ,NTSC(National Television System Committee)サイズ,サムネイル・サイズといった解像度の異なる画像に伸張して,同時に出力・表示するボードである.このボードには,ISSPチップが4個搭載されている.NECエレクトロニクスによると,本チップの開発の終盤では何度も仕様の変更が発生したが,ストラクチャードASICは短納期であるため,数日で作り直すことができたという.

[写真2] アイ・シーが開発したJPEG2000デコーダ・ボード

放送業務用ボード.NECエレクトロニクスのISSPが四つ搭載されている.設計手法は,基本的に従来のASICと同じである.

一方,東芝は,ストラクチャードASICとコンセプトがよく似た「UniversalArray」と呼ぶASIC製品を発表した.通常のストラクチャードASICの場合,搭載するIP(intellectual property)コアの機能やメモリ容量,I/Oマクロが異なる何種類かのマスタ・スライス(下地)をあらかじめASICベンダが用意している.一方,UniversalArrayの場合,東芝は特定のマスタ・スライスを用意しない.個々のユーザが要求するカスタム仕様のマスタ・スライスを開発する.マスタ・スライスの試作と並行して詳細レイアウト設計やタイミング検証を実施するため,セル・ベースICと比べて開発期間を短縮できる.また,仕様の変更や設計修正が発生した場合の追加コストも少なくて済むという.

●UMLとSystemCを活用したシステムLSI設計の成果を披露

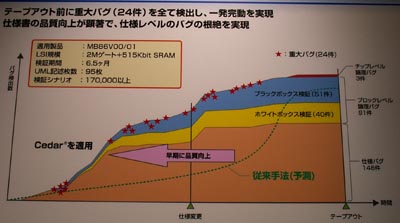

富士通は,UML(unified modeling language)とSystemCを導入することで検証の網羅性を上げる「Cedar」という手法を開発し,これを利用したコンサルティング事業を開始している.本展示会では,この手法を利用した最初の製品である「MB86V00/01」を展示した(写真3).現段階では,顧客によるCedarの導入事例はまだないという.

本手法を用いるには,UMLで書かれた仕様を読み取るスキルが必要になる.回路設計者はこれをもとに,RTL(register transfer level)で設計を行う.UMLをもとに作成したSystemCのシミュレーション結果とRTLデータのシミュレーション結果が一致すれば,仕様と設計の間の整合がとれていることになる.例えばMB86V00/01の開発では,仕様上のバグが早期に見つかり,テープアウト前にすべての重大なバグを検出することができたという(写真4).

[写真3] 画像処理LSI「MB86V00」と「MB86V01」

CPUコア(ARM7TDMI)やJPEG/MPEG-4 CODEC(coder/decoder),LCD(liquid crystal display)コントローラ,カメラ・インターフェースなどを内蔵した携帯電話向け画像処理LSI.MB86V00については,64MビットSDRAMも同一のパッケージに封止されている.

[写真4] Cedarの適用効果

画像処理LSI「MB86V00」,「MB86V01」にCedarを適用した際のバグ曲線.

●高位の仕様をプロパティとして入力できる形式的検証ツールを展示

米国Jasper Design Automation社は,自動分割機能を組み込むことにより,比較的規模の大きい回路(状態数の多いモデル)を取り扱えるプロパティ検証ツール(形式的検証ツール)「JasperGold」を展示した(写真5).本ツールは,検証対象となる設計データの状態遷移モデルを分割する機能「PreCognitive Engine」と,分割された各状態遷移モデルに対してプロパティ検証を実施する「Proof Engine」を内蔵している.従来のプロパティ検証ツールでは,取り扱える回路規模に制約がある場合が多かったが,本ツールにはこうした制約がないという.また,大規模な回路を扱えるようになったため,抽象度の高い仕様(シンプルなビヘイビア・モデル)をプロパティとして設定することが可能となった.例えば,最初は抽象度の高いプロパティを使って広範囲の動作に影響を与えるバグを検出し,その後,抽象度の低いプロパティを使って特定の動作にのみ影響を与えるバグを探索するといった手法がとれる.

検証対象となる設計データの記述言語として,Verilog HDLとVHDLに対応している.プロパティは独自の言語で記述する.次バージョンではAccellera標準のPSL(Property Specification Language)に対応する予定.

また,プロパティとの不一致を検出した際に,原因となる箇所を波形を見ながら対話的に探索できるデバッグ環境を用意した.信号波形と対応するHDL記述の間のクロス・プローングを行える.さらに,標準的なバス・プロトコルについて,プロパティのテンプレートが用意されている.

本ツールは,Solaris 2.8/2.9,RedHat Linux 7.3/8.0,同Enterprise 3.0の上で動作する.

[写真5] JasperGoldの画面例

デバッグ環境の信号波形のウィンドウ.HDL記述のウィンドウとクロス・プロービングを行える.

●3Gbpsの伝送速度のSerial ATAに対応したPHYチップのデモを実施

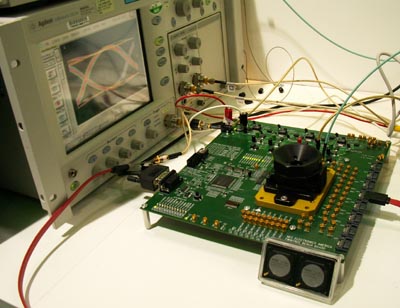

NECエレクトロニクスのブースでは,Serial ATA Generation2に対応したPHY(物理層)チップのデモンストレーションが行われた.データ転送速度が3Gbpsの信号のアイ・パターンを確認した(写真6).

同社はすでに,データ転送速度が1.5GbpsのSerial ATA Generation1のPHYのIPコア「SATAll-p1」を提供しており,本IPコアを採用したLSIが量産されているという.また,3GbpsのSerial ATA Generation2に対応したPHYのIPコア「SATAll-p2」を採用したLSIについては,2005年春ごろから量産が開始されるという.いずれのIPコアもハード・マクロで,0.15umと0.13umの製造プロセスに対応している.また,リンク層とトランスポート層のソフト・マクロのIPコアを用意する.

現在,同社は90nmと65nmの設計ルールに対応したSerial ATAのPHY IPコアを開発中である.2005年秋ごろには試作チップ(ファースト・シリコン)ができ上がる予定.このIPコアを搭載したASICの量産出荷は,2006年ごろに開始されるもよう.

[写真6] Serial ATA Generation2対応のPHYチップのデモンストレーション

3Gbpsのデータ転送速度の信号のアイ・パターンを測定している.

●Accellera,2006年にSystemVerilogミックスト・シグナル拡張版を標準化

米国Accelleraは,設計・検証言語であるSystemVerilogに関して,2006年ごろにミックストシグナル拡張版の「SystemVerilog-AMS」の標準化を予定していることを明らかにした(写真7).AccelleraはEDAベンダや半導体メーカなどが参加する業界団体で,EDAツールに関する標準化活動や普及推進活動を行っている.

Accelleraは昨年(2004年),Verilog-AMSのバージョン2.2とCompact Modelの仕様を策定し,今年(2005年)の2月にAccellera標準として承認している.Compact Modelとは,トランジスタやダイオードといった半導体素子の特性を記述するトランジスタ・レベルのビヘイビア・モデルの規格である.

Accelleraは今年,これら二つの仕様を一つにまとめたVerilog-AMSバージョン2.3を策定し,さらに2006年ごろにはこれらとSystemVerilogを統合したSystemVerilog-AMSの仕様を策定することを計画している.SystemVerilogは同組織が承認したVerilog HDLの拡張仕様で,2005年中にIEEE標準(IEEE 1800)になるという.

このほか,Accelleraは2005年内に,回路ライブラリ・フォーマットの規格であるALF(Advanced Library Format)とLiberty(.lib)の機能や用語の対応をとるためのドキュメント(クロス・リファレンス)を作成する.ALFはAccelleraが標準化したライブラリ・フォーマット,Libertyは米国Synopsys社が開発し,一般公開しているライブラリ・フォーマットである.クロス・リファレンスを提供することにより,LibertyのユーザがALFへ移行しやすくなるという.

[写真7] EDS Fair 2005に合わせて来日したAccellera,ChairmanのDennis B. Brophy氏

SystemVerilogミックスト・シグナル拡張版の仕様策定を計画している.