ディジタル信号処理をハードウェア化する開発環境が充実 ――Global Signal Processing Expo(GSPx)

2004年9月27~30日,ディジタル信号処理システムの開発に関する展示会/研究会「2004 Global Signal Processing Expo and Conference(GSPx)」が,米国カリフォルニア州Santa ClaraのSanta Clara Convention Centerで開催された(写真1).展示会場では,ディジタル信号処理システムの開発環境やDSP(ディジタル信号処理プロセッサ)ボード,DSPコア,FPGAなどのベンダがデモンストレーションを行った.

ディジタル信号処理アルゴリズムをシステムLSIやASIC(application specific integrated circuit),FPGA(field programmable gate array)に実装するためのツールの展示が相次いだ.

[写真1] 2004 Global Signal Processing Expo and Conference(GSPx)の会場

GSPxは,米国カリフォルニア州Santa ClaraのSanta Clara Convention Centerで開催された.

●浮動小数点演算を固定小数点化する作業を自動化

米国Catalytic社は,米国The MathWorks社の信号処理システム設計ツール「MATLAB」で作成した浮動小数点モデルを固定小数点モデルに変換する開発環境「Fixed-Point DSP Studio」を展示した(写真2).固定小数点DSP用のソフトウェア開発や,FPGA,ASICの開発などに利用できる.

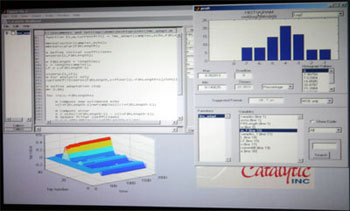

[写真2] Catalytic社の「Fixed-Point DSP Studio」の画面例

浮動小数点モデルを固定小数点モデルに変換する作業を支援する.

本ツールは,浮動小数点モデルを固定小数点モデルに変換するソフトウェア,ディジタル信号処理システムのシミュレータ,固定小数点モデルを解析し,その結果をグラフィカルに表示するソフトウェアからなる.本ツールでは,独自の固定小数点データ型を用意している.これを利用することにより,MATLABと比べて5~10倍程度高速にシミュレーションを行えるという.

入力となる浮動小数点モデル,および出力となる固定小数点モデルのフォーマットはMATLABのMファイル.Windows 2000/XPが稼働するパソコン上で動作する.2004年10月中に出荷を開始する予定.

●合成ツールはディジタル信号処理用ライブラリを拡充

米国AccelChip社は,同社のビヘイビア合成用ライブラリ「AccelWare」の機能ブロック(IPコア)のラインナップを拡充した.AccelWareは,ASICやFPGAに組み込むディジタル信号処理回路を開発するためのライブラリで,同社のディジタル信号処理向けビヘイビア合成ツール「AccelChip DSP Synthesis」と組み合わせて利用する(写真3).

[写真3] AccelChip社のブース

同社は,ディジタル信号処理回路を設計するためのビヘイビア合成ツールとそのライブラリのデモンストレーションを行った.

今回,新たにビタビ・デコーダ,多相デシメーション・フィルタ,ガロア体演算,基数4のFFT(fast Fourier transform)演算,離散FIR(finite impulse response)フィルタ,高速除算などの機能ブロックを用意した.例えば,ワイヤレス通信,ソフトウェア無線,GPS(Global Positioning System),レーダ,ソナーなどの機器に搭載するASICやFPGAの開発に利用できる.

AccelWareの機能ブロックは,パラメータ設定によって機能をカスタマイズできるようになっている.また,ビヘイビア合成時に最適な回路が生成されるように,回路構造の制約情報が含まれている.

一方,米国Synplicity社は,同社の論理合成ツールと固定小数点ライブラリを組み合わせた開発ツール「Synplify DSP」を展示した.The MathWorks社のディジタル信号処理システム設計ツール「Simulink」とのインターフェースを備えている.

●MATLAB/Simulinkの競合ツールが存在を誇示

ディジタル信号処理や通信向けのシステム設計ツールの市場では,The MathWorks社の「MATLAB/Simulink」が圧倒的なシェアを獲得している.本展示会では,同ツールの置き換えをねらう製品をいくつかのベンダが展示した.

米国Elanix社は,同社のディジタル信号処理システム設計ツール「SystemView」と組み合わせて使う固定小数点ライブラリ「FXP-Lib」のデモンストレーションを行った(写真4).固定小数点モデルの解析ツールを備えており,ダイナミック・レンジやオーバフロー/アンダフロー,ヒストグラムなどを確認しながら,信号のビット幅などを決定できる.DSP用のソフトウェアやASIC,FPGAなどの開発に利用できる.

[写真4] Elanix社のブース

固定小数点ライブラリのデモンストレーションを行った.これを利用すると,固定小数点アルゴリズムをソフトウェアやLSIに実装する時間が短くなるという.

FXP-Libはサイクル精度のシミュレーション用ライブラリである.加算,減算,乗算,除算,平方根,FIRフィルタ,シフタ,フォーマット変換,ビット抽出,参照テーブル,比較器,ANDゲート,NOTゲート,ORゲート,XORゲート,定数,遅延,ビット結合などの機能ブロックから構成されている.今後,MAC(multiplier and accumulator)やアキュムレータ,マルチプレクサ,デマルチプレクサ,FFTなどの機能ブロックも提供する予定.HDL Design Studioというオプションを利用すると,FXP-Libを利用して作成した固定小数点モデルからRTL(register transfer level)のVHDLコードやテストベンチ,EDAツール用スクリプトを生成できる.

一方,米国CoWare社は,今回の展示会に合わせて,同社のディジタル信号処理システム設計ツール「SPW」のWindows XP版「SPW5-XP」を発表した.2004年11月に出荷を開始する.

CoWare社のSPWの事業は,2003年9月に米国Cadence Design Systems社から移管された.CoWare社は,従来のUnix版やLinux版に加えて,Windows版も提供していく方針.従来,SPWは主にASICやシステムLSIなどの開発に利用されてきた.安価なWindows版の提供により,今後はDSPのソフトウェア開発やFPGA設計への浸透を図っていきたいという.

●C言語ハード・ソフト協調合成の実用化を目指す

最近では,ハードウェア(回路)とソフトウェアの両方を考慮して,最適なシステム構成を実現する開発環境が続々登場している.汎用的に適用することは難しいが,応用をディジタル信号処理に絞れば,実用レベルに達しつつあるようだ.

米国Poseidon Design Systems社は,ビヘイビア合成ツール「Triton Builder」とシステムLSIの性能解析ツール「Triton Tuner」のデモンストレーションを行った(写真5).CPUコアを内蔵するASSP(application specific standard product)やASIC,FPGAなどの開発に適用できる.

[写真5] Poseidon Design Systems社のデモンストレーションのようす

FPGAをターゲットとするデモンストレーションを行った.

Triton Builderの入力はC言語のアルゴリズム記述(アプリケーション・コード)とハードウェアのアーキテクチャ情報である.ユーザは,まず,アルゴリズム記述を実行してプロファイルを取り,性能向上のボトルネックとなっている箇所を見つけ出す.次に,この部分を高速に処理するアクセラレータ回路をビヘイビア合成によって生成する.アクセラレータ回路のRTL記述のほか,デバイス・ドライバやシステム・プロファイル・レポートなども合わせて出力する.

一方,Triton Tunerは,プロセッサ・コア,命令キャッシュ,データ・キャッシュ,2次キャッシュ,周辺の機能ブロック,オンチップ・バスからなるLSIを対象とする解析ツールである.アルゴリズム記述のプロファイルを取ったり,メモリの使用率や性能,キャッシュの性能などを解析する機能を備えている.また,トランザクション・レベルのSystemCモデル(SystemCシミュレーション環境)と接続して協調検証を行える.現在,対応しているプロセッサ・コアはARMと米国Xilinx社のMicroBlaze.今後はPowerPCや米国Altera社のNiosにも対応していく計画である.

また,米国Synfora社は,独自のVLIW(very long instruction word)プロセッサ・コアと,PPA(Pipeline of Processor Arrays)と呼ばれるアクセラレータ回路からなるアーキテクチャをターゲットとするビヘイビア合成ツール「PICO Express」のデモンストレーションを行った(写真6).入力はC言語のアルゴリズム記述,出力はPPAのRTL記述である.ビデオ・フィルタやMP3デコーダ,ビタビ・デコーダ,逆離散コサイン変換などの設計に適用したところ,人手で設計した場合と同等かそれ以上の性能を実現できたという.

[写真6] Synfora社のブース

ビヘイビア合成ツールのデモンストレーションを行った.PICOと呼ばれるこの技術は,米国Hewlett-Packard社の研究所で開発された.

●ポストFPGAをねらうデバイスを展示

米国MathStar社は,大規模な並列プロセッサ・アレイや1G~4.25GbpsのSerDes(serializer/deserializer)回路などを内蔵するプログラマブル・デバイス「FPOA(Field Programmable Object Array)」のデモンストレーションを行った(写真7).ゲート・レベルやRTLより高い抽象度で設計できるように,FPOAはFPGAよりも粒度(ゲート規模)の大きい回路ブロック(「Silicon Object」と呼ぶ)を多数内蔵している(最初に出荷された「SOA13D40」はSilicon Objectを400個内蔵).論理合成を行う必要がないため,FPGAやASICと比べて開発に時間がかからないという.また,ASICと異なり,タイミング収束の問題も生じない.その一方で,回路ブロックの粒度が大きいため,FPGAより高速に動作するという(内部クロックの最大動作周波数は1GHz).

[写真8] FPOAを搭載したMathStar社の評価ボード

FPOAは大規模な並列プロセッサ・アレイを内蔵するプログラマブル・デバイスである.システム・レベルの設計情報(SystemC記述など)を,直接,並列プロセッサ・アレイにマッピングできるという.

並列プロセッサ・アレイを構成する回路ブロックには,16ビットALU(arithmetic logic unit),パターン認識回路(小規模な連想記憶メモリ),MAC,レジスタ・ファイルの4種類がある.これらを組み合わせて,所望の機能を実現する.また,データ・バッファリングや定数記憶に利用する9KバイトのSRAMも搭載している.I/O回路としては,上述のSerDes回路のほか,DDRメモリ・コントローラや高速パラレルI/O,汎用I/O(GPIO)を備えている.

ユーザは,例えば米国Summit Design社のシステム・レベル設計ツール「Visual Elite」を使ってシステム機能のブロック図や状態遷移図を作成し,これをSystemCデータに変換する(Visual Elite用のライブラリがMathStar社から提供されている).そして,このSystemCデータをMathStar社の「COAST(Connect and Assign Silicon Object Array)」というツールに入力し,並列プロセッサ・アレイにマッピングする.さらに,その結果を同社の「FPOA Compiler」と呼ばれるツールに渡して,本デバイスのプログラム・データを生成する.

同社は,FPOAによってバス・ブリッジ回路やフィルタ回路を実現するためのライブラリも提供している.

過去の関連記事

・組み込み写真館:2004 Global Signal Processing Expo and Conference (GSPx)