No.2(2009・SUMMER) 目次

2009年7月 9日

特集

HDL設計超入門ブロック図を使ってラクラク理解 |

p.4 | ||

|---|---|---|---|

|

第1章 ディジタル機器の仕組みと開発手順――論理回路設計の位置付けを理解する |

浅井 剛 | pp.6-9 | |

|

第2章 初めて回路設計の仕事を与えられたら――3社のFPGAに対応するダウンロード回路の設計を模擬体験 |

井倉将実 | pp.10-19 | |

|

第3章 HDL時代に求められる論理回路設計とは――回路記号を使わない論理設計手法の考え方 |

小林 優 | pp.20-27 | |

|

第4章 論理回路の機能の表現法――ブロック図,真理値表,タイミング・チャートの活用 |

小林 優 | pp.26-40 | |

|

第5章 回路を構成する基本要素――セレクタ,エンコーダ/デコーダ,演算器,レジスタ,カウンタ |

小林 優 | pp.37-48 | |

|

第6章 論理回路設計の第一歩――24時間時計のカウンタ部を作りFPGAで動作させる |

小林 優 | pp.49-62 | |

|

第7章 論理回路設計の考え方――回路や出力信号の形式を整理する |

小林 優 | pp.63-74 | |

|

第8章 演算回路の設計法――乗算回路と1けた電卓 |

小林 優 | pp.75-87 | |

|

第9章 制御回路の設計法――状態遷移図とステート・マシンの活用 |

小林 優 | pp.88-99 | |

|

第10章 実用的な回路の設計――シリアル送受信回路と時刻合わせ機能付き時計回路 |

小林 優 | pp.100-116 | |

|

Appendix Verilog HDL記述の読み方 |

小林 優 | pp.117-118 | |

|

第11章 ディジタル回路を見直す――電子回路の基礎知識と論理回路とを結び付ける |

浅井 剛 | pp.119-127 | |

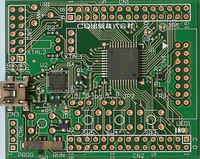

特集で紹介する回路を試せるFPGAボード――本特集をより深く理解するために |

編集部 | pp.2-3 |