[ keyword: CPU, IP, センサ ]

Cypress,ARM Cortex-M0コアを搭載するミックスト・シグナル・プログラマブル・デバイスの新アーキテクチャを発表

ニュース 2013年3月22日

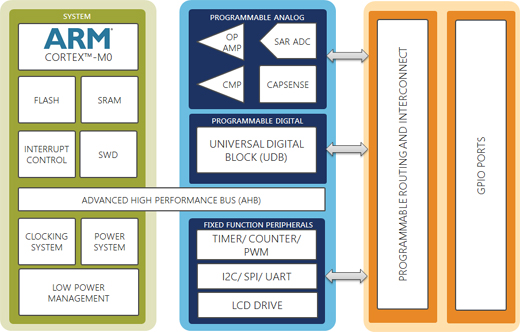

米国Cypress Semiconductor社は,ミックスト・シグナル・プログラマブル・デバイス「PSoC(Programmable System-on-Chip)」の新しいアーキテクチャ「PSoC4」を発表した.PSoCとは,OPアンプとスイッチト・キャパシタを利用する汎用のアナログ演算処理回路ブロック,FPGAと同じように内部の論理機能を変更できる汎用の論理ブロック,CPUコア,周辺機能などを集積した1チップ・マイコンである.

既存のPSoC3アーキテクチャはCPUとして8051コアを,PSoC5はARM Cortex M3コアを搭載していた.今回のPSoC4はARM Cortex-M0コアを搭載している.PSoC4のアナログ演算処理回路ブロックには,静電容量タッチ・センサ・コントローラ回路(CapSense)が組み込まれている.例えば,ベクトル制御モータを利用する機器や温度センサを利用する機器,セキュリティ機器,携帯型医療機器などの開発に適しているという.

待機時の消費電力は150nA,ウェイクアップ機能を維持した停止モードにおける消費電力は20nA.動作電圧範囲は1.71~5.5V.

本デバイスの開発には,同社の設計環境「PSoC Creator」を利用する.ユーザはPSoC Componentと呼ばれるアイコンを組み合わせて,グラフィカルな環境で設計を行う.

[図1] PSoC4の機能の概要

■価格 |

■連絡先 |