[ keyword: CPU, コンピュータ ]

富士通,SPARC64 Xを最大64個搭載するUNIXサーバの出荷を開始

ニュース 2013年1月18日

富士通は,同社のプロセッサ「SPARC64 X」を最大64個搭載するUNIXサーバ「SPARC M10」の出荷を開始した.SPARC64 Xは,16個のCPUコアを内蔵しており,サーバ全体では最大1024個のCPUコアが並列動作することになる.ビジネス系のデータ処理のほか,ビッグ・データの解析やリアルタイム・ビジネス解析,データウェア・ハウスの処理などにも利用できる.

SPARC64 Xプロセッサのクロック周波数は2.8GHzまたは3.0GHz.一つのCPUコアで二つのスレッドを実行可能.同社の従来機のプロセッサ(SPARC64 VII+)と比べて,CPUコア1個当たりの整数演算性能は約1.9倍に,プロセッサ1個当たりの整数演算性能は約7.5倍に向上した.また,データベース処理で多用する機能を高速に実行できる専用回路を搭載している.データベース用のマイクロベンチマークを実行したところ,10進演算処理は従来の430倍に,暗号処理は163倍に,コピー処理は12倍に,比較処理は15倍に,ハッシュ処理は7倍に高速化した.28nmのCMOSプロセスで製造する.

一つのSPARC64 Xプロセッサに対して,16枚のDIMM(Dual Inline Memory Module)を直結できる.プロセッサやメモリを冷却するため,自律型循環液冷システムを備えている.高信頼化のため,キャッシュ・メモリに加えて,整数/浮動小数点レジスタにもECC(誤り検出訂正)機能を付加した.また,演算器はパリティ予測機能を備えており,演算結果のパリティ比較が行えるようになった.

SPARC64 Xプロセッサを1個搭載する1Uラックマウントの「SPARC M10-1」,SPARC64 Xプロセッサを最大4個搭載する4Uラックマウントの「SPARC M10-4」,SPARC M10-4を最大16台接続できる「SPARC M10-4S」の3機種を用意する.筐体間の伝送速度は14.5Gbps.外部インターフェースにはPCI Express 3.0を利用する.必要な数だけCPUコアをアクティベート(活性化)する機能を備えており,ユーザが求める処理能力に合わせて2コア単位でサーバの性能を拡張できる.また,仮想化機能により,複数世代のSolaris OSの混在が可能.

SPARC M10-1とSPARC M10-4はすでに出荷中.SPARC M10-4Sは,2013年1月末より出荷を開始する.

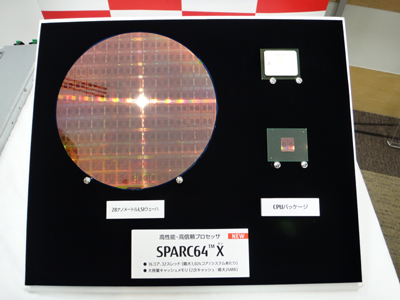

[写真1] SPARC64 Xプロセッサのウェハとパッケージ

[写真2] SPARC M10-4の筐体内部

[写真3] 自律型循環液冷システム(金色に着色された部分を冷却液が流れる.黒い部品はポンプ)

■価格 |

■連絡先 |