[ keyword: LSI, SoC, FPGA ]

BaySand,開発費が従来の1/10に,量産時のチップ単価がFPGAの1/10になるスタンダード・セルASICの日本での受注を開始

ニュース 2012年10月24日

米国BaySand社は,一部のメタル・マスク層の変更によって機能をカスタマイズするスタンダード・セル方式ASIC「TeneX」の日本での受注を開始した.こうした技術を,同社では「MCSC(Metal Configurable Standard Cell)」と呼んでいる.製作するマスクの枚数が減るので,開発費を従来のスタンダード・セル方式の1/10に抑えられる.また,量産時(例えば,年間5,000個を生産した場合)のチップ単価はFPGAの1/10になるという.

4種類の品種を用意する.すなわち,米国Altera社のFPGA(Stratix,Cyclone)とパッケージ/ピン互換性のある「TeneX-FA」,米国Xilinx社のFPGA(Virtex,Spartan)とパッケージ/ピン互換性のある「TeneX-FX」,I/Oピンの割り当てやI/Oバンクを柔軟に変更できるスタンダード・セル方式ASIC「Tenex-AS/AS+」,ASSP(Application Specific Standard Product)の開発プラットフォームとして提供する「TeneX-AP」である.

製作するメタル・マスク層(配線層)の数を減らすと,一般には配線の自由度が下がり,ダイ・サイズ(チップ面積)が大きくなりがちである.同社では,回路ブロックや配置配線の最適化によってダイ・サイズの増加を抑えているという.

例えば,回路ブロックのI/Oピンを引き出す方向の制約をなくし,回路ブロック間の配線長を短縮しやすくした.これにより,配線に挿入するバッファ回路の数が減り,ダイ・サイズが小さくなる.また,複雑な経路を通る配線が減るので,必要なシグナル・インテグリティ(信号品質)対策が減り,回路が簡素になる.さらに,あらかじめ用意されているメモリ・ブロックについて,ユーザがデュアルポートかシングル・ポートかを選択できるようにした.これにより,使用しない(無駄な)メモリ領域が減った.このほか,使われていないメモリ領域の一部を,必要に応じて論理回路として利用できるようにした.I/Oブロックについても,回路上の工夫により,従来の半分のサイズで実現できるようにした.これらの最適化の組み合わせにより,ダイ・サイズは従来のスタンダード・セル並み,あるいはそれ以上に小さくできるという.

製造プロセスは65nm,ファウンドリは米国GLOBALFOUNDRIES社.BaySand社によると,東芝のプロセスで製造することも検討しているという.

ユーザはRTLデータ(Verilog HDLまたはVHDL)とタイミング制約ファイル(SDC)を同社に引き渡す.機能設計には,Design Compilerなどの市販の論理合成ツールを利用する.同社が提供する変換ツール(プリプロセッサ,テクノロジ・マッピング・ツール)を市販の論理合成ツールと組み合わせて使用する.ユーザがMCSCの構造を意識する必要はない.

国内販売代理店は丸文.

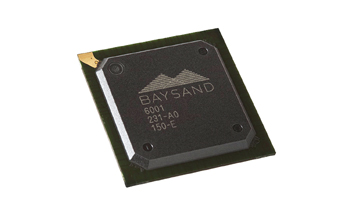

[写真1] TeneXの外観

■価格 |

■連絡先 |