[ keyword: EDA, パッケージ, LSI ]

Synopsys,シリコン貫通電極やシリコン・インターポーザを使用したスタック型SiPの設計環境を包括的に提供

ニュース 2012年3月28日

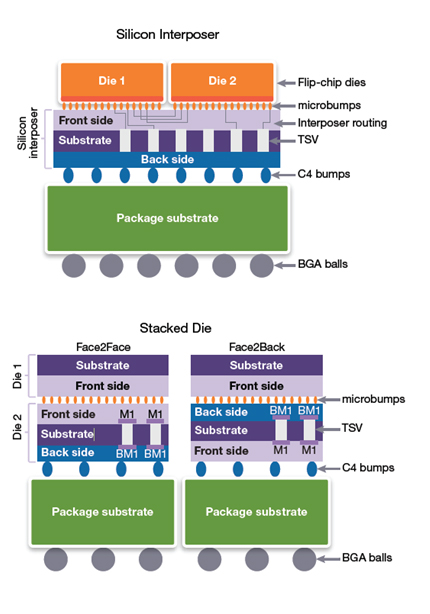

米国Synopsys社は,スタック型SiP(System in Package)の設計環境を整備・強化し,包括的に提供することを発表した.シリコン貫通電極やシリコン・インターポーザ(シリコン基板)を用いて複数のフリップ・チップを積層したマルチチップ・モジュールが対象となる.同社ではこうした取り組みを「3D-IC Initiative」と呼んでいる.

最近ではデータ伝送のバンド幅を広げたり,消費電力を押さえたりするために,メモリ・ダイを積層したSiPが開発されている.また,実現できる回路規模を大きくするため,シリコン・インターポーザ上に四つのFPGAダイを積層したモジュールも製品化されている.本設計環境は,こうしたスタック型SiPの開発に利用できる.

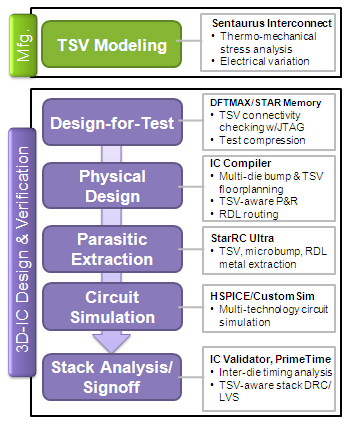

本設計環境は以下の10個のツールで構成される.すなわち,積層するダイやシリコン貫通電極の検査を支援するテスト容易化設計ツール「DFTMAX」,メモリ・ダイのテストや診断などを行うIPコア「DesignWare STAR Memory System IP」,シリコン貫通電極や微小バンプの配置,シリコン・インターポーザ内部の配線,電源メッシュの生成,配線チェックなどに対応した配置配線ツール「IC Compiler」,シリコン・インターポーザなどの金属配線の寄生容量などを解析する寄生容量抽出ツール「StarRC Ultra」,積層したダイの配線における信号品質を解析する回路シミュレータ「HSPICE」および「CustomSim」,IRドロップとエレクトロマイグレーションの解析ツール「PrimeRail」,シリコン貫通電極や微小バンプの設計ルール・チェックや回路チェックが行えるレイアウト検証ツール「IC Validator」,シリコン・インターポーザの配線や電源メッシュを人手で編集できる配置配線ツール「Galaxy Custom Designer」,熱や物理ストレスを解析できる配線ストレス/信頼性解析ツール「Sentaurus Interconnect」である.それぞれのツールといっしょに利用するライブラリを,スタック型SiPに対応させた.一方,同社が持っていないパッケージ基板設計ツールなどはこの設計環境には含まれていない.

同社では,上述の設計環境について,ベルギーのIMEC(Interuniversity Microelectronics Centre)や台湾のITRI(Industrial Technology Research Institute)と共同開発を行っているという.スタック型SiPの設計環境については,現在,特定顧客にベータ版を提供中.2012年第2四半期に一般顧客向けの出荷を開始する予定.

[図1] フリップ・チップを積層するSiP

[図2] Synopsys社のスタック型SiP向け設計環境

■価格 |

■連絡先 |