[ keyword: EDA, IP, SoC ]

SynopsysがSystemVerilogの検証用IPを一新,ラッパや変換が不要になり検証速度が約4倍に向上

ニュース 2012年3月7日

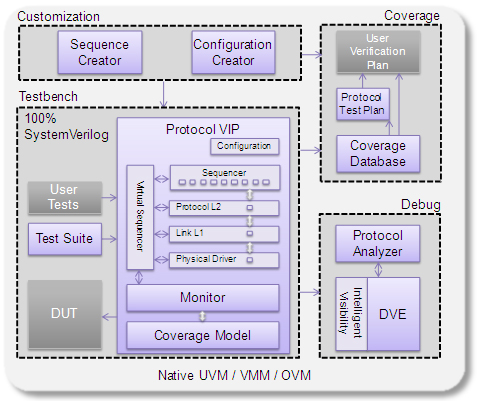

米国Synopsys社は,「VIPER」と呼ぶ新しいアーキテクチャに基づいて,同社の検証用IPを作り直した.新しい検証用IPは「Discovery VIP」という名称で,対応言語はSystemVerilogのみ.検証用モデルにラッパ(インターフェース・プログラム)を追加したり,変換などを行ったりせず,SystemVerilogのネイティブ・コードで動作する.これにより,検証速度が約4倍に向上するという.

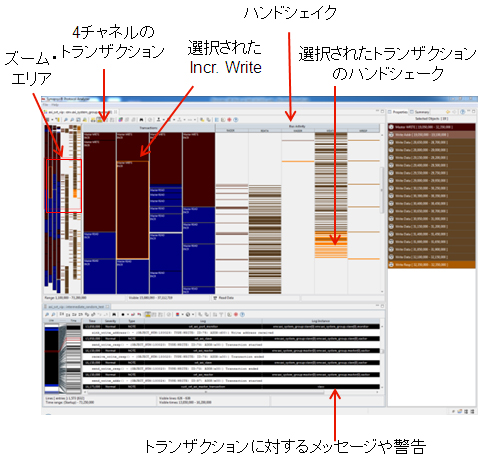

本検証用IPは,LSIの入出力信号(外部バス)およびLSI内部のブロック間信号(オンチップ・バス)の通信プロトコルの検証,および標準インターフェース回路ブロックのコンプライアンス・テストなどに利用できる.トランザクションの流れをグラフィカルに表示するプロトコル・アナライザ機能や,標準的な通信プロトコルの仕様を自動設定する機能を備えている.また,それぞれの通信プロトコルに対応したテスト・プラン(検証項目)があらかじめ用意されている.

同社は,AMBA 4/3/2,USB 3.0/2.0/1.1/OTG,HDMI 1.4,Ethernet(10M~100G),Interlaken,SPI 4.2,RS-232,GPIO,IrDA,OCP 2.2/2.1/2.0,I2C,SDIO,MIPI CSI/DSI/DigRF v4/HSI,PCI Express Gen3/2/1,PCI/PCI-X 2.0/1.1,SR-IOV,Serial ATA 1.5/3.0/6Gbps,SAS,ATAPI,DDR3/2,UARTといった検証用IPを出荷している.これらのすべてを,順次,VIPERアーキテクチャに対応させていくという.

本検証用IPは,UVM(Universal Verification Methodology),VMM(Verification Methodology Manual),OVM(Open Verification Methodology)のいずれの検証手法および検証用ライブラリにも対応している.機能シミュレータについては,同社の「VCS」のほか,米国Cadence Design Systems社の「Incisive」と米国Mentor Graphics社の「Questa」をサポートする.

[図1] VIPERアーキテクチャ

[図2] プロトコル・アナライザ機能の画面例

■価格 |

■連絡先 |