[ keyword: EDA, SoC, 開発手法 ]

Synopsys,5億インスタンスのフルチップ解析に対応した静的タイミング解析ツールを発売

ニュース 2010年6月15日

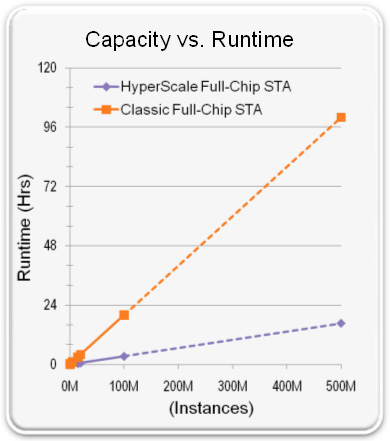

米国Synopsys社は,静的タイミング解析ツールの新バージョン「PrimeTime 2010」を発売する.今回のバージョンでは,5億インスタンスのフルチップ解析に対応できるようになった.また,フルチップ解析の処理にかかる時間を従来の1/5~1/10に短縮したという.

大規模な回路を高速に処理するため,ブロック・レベルのタイミング解析の結果をフルチップ解析に利用できるようにした.各ブロック内部のパスの伝播遅延時間をあらためて計算する必要がないので,フルチップ解析にかかる時間を短縮できる.こうした手法を,同社では「HyperScale」と呼んでいる.四つのCPUコアを搭載するサーバを使い,1500万インスタンスの回路のタイミング解析を行ったところ,従来手法では176分かかった.一方,今回のHyperScale手法を利用すると22分で処理が完了したという.

本ツールは,現在,PrimeTime SI 2010.06バージョンとして限定顧客向けに提供中である.

[図1] HyperScale手法と従来手法の実行時間の比較

■価格 |

■連絡先 |