[ keyword: EDA, LSI, 開発手法 ]

Synopsys,45nm以降の設計ルールの増加や複雑化に対応できる高速なレイアウト検証ツールを発売

ニュース 2009年5月12日

米国Synopsys社は,45nm以降の設計ルールの増加や複雑化に対応できる高速なレイアウト検証ツール「IC Validator」を発売した.レイアウト設計後の最終的な検証(サインオフ検証)に利用できる.また,同社のレイアウト設計ツールである「IC Compiler」に組み込むことで,レイアウト設計の過程で逐次実施する検証にも利利用できる.

レイアウト検証ツールは,レイアウト・パターンの幾何的な形状(例えばセル間の距離や配線幅など)が製造上求められる制約に合致しているかどうかをチェックするDRC(Design Rule Check)や,レイアウト・データと回路図の接続の間に不整合がないかどうかをチェックするLVS(Layout vs Schematic)などから構成される.プロセスの微細化に伴って,DRCのルール数は増加している.例えば32nmのプロセスでは1200以上のルールをチェックしているという.また,ルールそのものが複雑になっている.32nmプロセスになると,メタル密度やポリシリコンの平たん性にかかわるルールが新たに加わった.

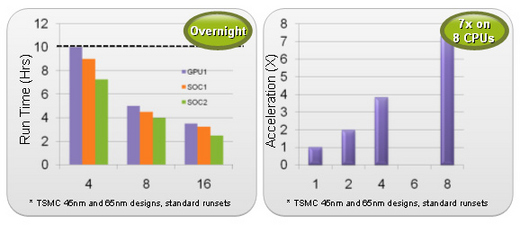

本レイアウト検証ツールは,こうした設計ルールの増加に対応するため,マルチコアやマルチスレッドといった並列処理を利用して処理速度を向上する.タスク分割は自動で行われ,複数CPUによる負荷分散が実施される.分割方法には,コマンド記述(ランセット)を分割して各CPUに割り当てる方式と,チップのレイアウトを分割してそれぞれのサブレイアウトを各CPUに割り当てる方式がある.例えば8CPUを搭載するコンピュータを使用すると,処理速度は1CPUの場合の約7倍に向上したという.

設計ルールはPXL(Physical Verification Specific Language)と呼ぶ言語を使って記述する.マクロ表現などを利用することで,設計ルールをコンパクトに,再利用しやすい表現で記述できるという.

米国NVIDIA社や台湾TSMC(Taiwan Semiconductor Manufacturing Company)などが,本レイアウト検証ツールを利用している.

[図1] IC ValidatorにおけるCPU数と処理速度の関係(Synopsys社の発表資料より)

■価格 |

■連絡先 |