[ keyword: LSI ]

Lattice,待機時電流が標準10μAのCPLDを発売

ニュース 2008年5月2日

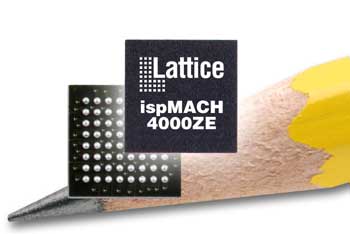

米国Lattice Semiconductor社は,待機時電流が標準10μAのCPLD「ispMACH 4000ZEファミリ」を発売する.32~256マクロセルの4品種を用意する.電源電圧は1.6V~1.8V.低消費電力が要求される携帯型機器などに利用できる.

未使用の入力端子を不能状態にできる(パワー・ガード機能).これにより,当該端子のスイッチ動作によるダイナミック消費電力を削減可能.また,端子ごとのプルアップ/プルダウン機能やバス・キーパ制御機能,入力ヒステリシス機能などを備えている.さらに,発振器やタイマ,JTAGインターフェースを内蔵する.

本CPLDには二つのI/Oバンクがあり,それぞれのバンクに個別の電源電圧を適用できる.入出力インターフェース・レベルは3.3V,2.5V,1.8VのLVTTL,およびLVCMOSに対応する.

パッケージは,64ピンと144ピンのCSP(chip size package),および48ピン,100ピン,144ピンのTQFP(thin quad flat package)を用意する.CSPのピン・ピッチは0.5mm.

本CPLDの設計には,同社の開発ツール「ispLEVER」を利用する.32マクロセル品と64マクロセル品のサンプル出荷は,既に開始している.全品種について,2008年半ばまでに量産出荷を開始する予定.

[写真1] ispMACH 4000ZEファミリの外観

■価格 |

■連絡先 |