[ keyword: 開発環境 ]

Xilinx,FPGAや組み込みソフトウェア,ディジタル信号処理の開発環境を一括提供へ

ニュース 2008年3月27日

米国Xilinx社は,同社のFPGA用開発環境の新版「ISE Design Suite 10.1」を発売した.従来,FPGAに実装する回路設計ツール(ISE Foundation,ISE WebPACK),FPGA内部のCPUコア上で実行する組み込みソフトウェアの開発ツール(Platform Studio,EDK),ディジタル信号処理システムの開発ツール(System Generator for DSP,AccelDSP)などを個別に提供していた.例えば,まず回路設計用ツールが供給され,数カ月遅れて組み込みソフトウェアの開発ツールが提供されていた.今回のバージョンから,これらの開発ツールを一括して提供する.

回路設計については,アルゴリズムの最適化により,動作速度を従来より8%程度改善できる.例えば,クリティカル・パスになりやすい乗算器やブロックRAMにつながるネットを検出し,優先的にタイミングを調整する.また,バス構成を意識してI/Oピンの配列を決定するようにした.

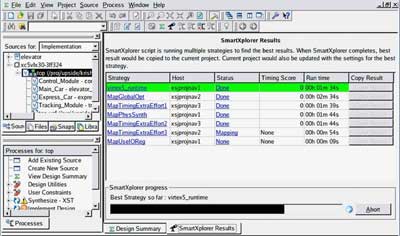

自動レイアウトにおいては,いろいろなオプション(ユーザが与える設計制約)の組み合わせが考えられ,それによって配置配線結果が変わる.今回のバージョンでは,複数台のコンピュータ(Linuxマシン)による分散処理を利用して,異なるオプションの組み合わせを与えながら複数のレイアウト処理を行う機能「SmartXplorer」を用意した.例えば15種類の配置配線結果の中から最適なものを選択することにより,FPGAの動作速度を最大38%高速化できたという.また,配置配線のオプションを自動選択する機能も用意した.

さらに,従来オプションであったフロアプランナ「PlanAhead」の機能限定版である「PlanAhead Lite」を標準搭載している.本ツールは,ピン割り当てや同時スイッチング解析,設計ルール・チェック,プリント基板設計ツールへのピン情報の受け渡しなどの機能を備える.静的タイミング解析の機能を利用する場合は,有償オプションのPlanAheadが必要になる.

このほか,消費電力低減のための機能(XPower Analyzer)も用意した.例えば,論理合成の際に,乗算器のパイプラインの段数を調整して消費電力を低減できる.また,配置配線の際にはトグル・レートをチェックして電力消費の大きいネットを検出し,最適化する.この機能を利用することで,ダイナミック消費電力を10~12%低減できるという.

[図1] ISE Design Suite 10.1の画面例(SmartXplorer)

■価格 |

■連絡先 |