[ keyword: I/F ]

アバールデータ,x4レーン対応のPCI Expressバス・ブリッジLSIを発売

ニュース 2007年11月6日

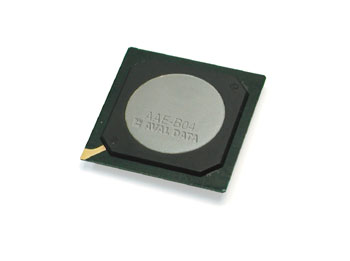

アバールデータは,PCI Expressバス・ブリッジLSI「AAE-B04」の受注を開始した.本LSIは,フラッシュROMやDDR SDRAM,FPGAと組み合わせて利用する.PCI Expressの基本機能として,物理層,データリンク層,トランザクション層の処理回路を備えている.対応するレーン数はx4(ピーク帯域は1Gバイト/s).画像処理や高速データ通信などのシステムに利用できる.

PCI Expressの基本機能のほか,DDR400に対応したメモリ・コントローラやローカル・バス・コントローラ,2チャネルのDMA(direct memory access)コントローラ,FPGA用のコンフィグレーション・ポート,I2Cシリアル・インターフェースなどを搭載する.ローカル・バスについては,チップ間接続に特化したシンプルな仕様を採用した.信号レベルは2.5V LVTTL(シングルエンド),バス幅は64ビット,バス・クロック周波数は133MHz.データ帯域は最大1.06Gバイト/s.外付けのFPGAには,ローカル・バスのインターフェース回路を組み込む必要がある.FPGA用のコンフィグレーション・ポートは,米国Altera社,米国Lattice Semiconductor社,米国Xilinx社のFPGAに対応する.

電源電圧は3.3V,2.5V,1.2V.672ピンの薄型プラスチックBGAに封止する.2007年11月中旬にサンプル出荷を開始する.量産出荷は2008年3月下旬から.

[写真1] AAE-B04の外観

■価格 |

■連絡先 |