[ keyword: EDA ]

Calypto,クロック・ゲーティングによって低消費電力化できる箇所を静的に解析するソフトウェアを発売

ニュース 2007年3月26日

米国Calypto Design Systems社は,クロック・ゲーティング手法によって低消費電力化できる箇所を静的に解析するソフトウェア「PowerPro CG」を発売した.本ソフトウェアを実際のディジタルLSIの設計データに適用したところ,3次元グラフィックス回路については31~61.1%,ネットワーク回路では58%,マイクロプロセッサでは20~22.7%,低消費電力化できることを確認したという.

入力は,Verilog HDLまたはVHDLのRTL(register transfer level)データ,タイミング制約情報(SDC:Synopsys Design Constraints),トグル情報(SAIF:Switching Activity Format),回路ライブラリ(.lib).これらの情報をもとに,各信号パスにクロック・ゲーティング手法を適用したときの消費電力の増減を計算する.また,各信号パスにクロック・ゲーティングを施す際に挿入するクロック制御回路(ゲーテッド・クロック回路)のデータも生成する.

米国Synopsys社のPower Compilerなど,いくつかの論理合成ツールは,消費電力を考慮してゲーテッド・クロック回路を自動挿入する機能を備えている.こうしたツールの多くは,組み合わせ論理とその後のフリップフロップの間に位置するセレクタ(イネーブル信号)を目安に,ゲーテッド・クロック回路の挿入可能箇所を特定しているという.すなわち,組み合わせ論理の回路構造を解析して,ゲーテッド・クロック回路を挿入できる箇所を検出している.

一方,本ソフトウェアでは,フリップフロップをまたいだ前段および後段の回路(パイプラインの前後のステージ)についても,前後のクロック・サイクルにおけるデータ信号の利用状況を考慮しながら,ゲーテッド・クロック回路を挿入できる箇所を探索している.すなわち,順序回路を対象に,ゲーテッド・クロック回路の挿入可能箇所を解析している.これにより,上述の論理合成ツールを使用した場合よりもさらに電力消費の少ない回路を見つけることができるという.

本ソフトウェアは,Linuxが稼働するパソコンの上で動作する.ゲーテッド・クロック回路の挿入前・挿入後におけるRTLデータの論理等価性を検証する等価性チェッカ(SLEC CG)も用意する.

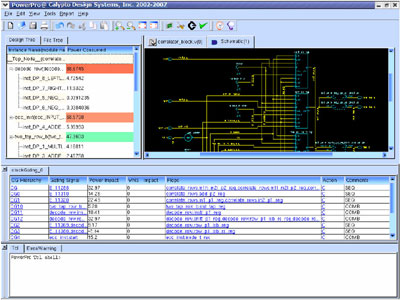

[図1] PowerPro CGの画面例

■価格 |

■連絡先 |