[ keyword: CPU ]

Stretch,ユーザが手元でカスタム命令を追加できるPLD内蔵32ビットRISCプロセッサを発売

ニュース 2004年4月27日

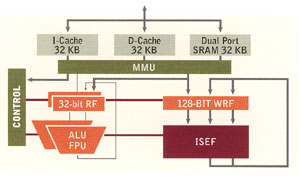

米国Stretch社は,ユーザが手元でカスタム命令を追加できる32ビットRISCプロセッサ「S5000ファミリ」を発売する.CPUコア(S5 Engine)の内部に,プログラマブル論理で構成されたデータパス回路(ISEF:Instruction Set Extension Fabric)を組み込んだ.例えば,ISEFにTripleDES暗号や色空間変換の回路を実装することで,これらの処理を1命令で実行できるプロセッサ(一種の特定用途向けDSP)になる.カスタム命令の処理(関数)はC/C++で定義する.ISEFに実装する論理回路をHDLなどを使って設計することはできない.このような構成のプロセッサを,同社は「Software Configurable Processor」と呼んでいる.

本プロセッサのCPUコアは,米国Tensilica社のコンフィギャラブル・プロセッサ・コア「Xtensa」をベースとしている.CPUコアの動作周波数は最大300MHz.命令キャッシュ,データ・キャッシュ,デュアルポートSRAMを,それぞれ32Kバイトずつ内蔵している.また,MMU(memory management unit)やFPU(floating-point processing unit)のほか,PCI/PCI-X,10M/100M/ギガビットEthernet,UART,HDLC(high level data link control),SPI(serial parallel interface),GPIO(general purpose input/output)などのインターフェース回路を備えている.ISEFは128ビット幅の入力ポートを三つ備えており,128ビットのレジスタ・ファイルからデータを受け取ることができる.

ユーザはまず,C/C++のプログラム・コードをコンパイルし,本プロセッサの実行プロファイルを取って,負荷の大きい処理を洗い出す.次に,この処理をカスタム命令として定義し,再度,実行プロファイルを取る.負荷の大きい処理を順番にカスタム命令化していき,所望の性能に到達したら,ISEFのコンフィギュレーション・データ(ブート・イメージ)を生成する.

Cコンパイラや命令セット・シミュレータ,アセンブラ,プロファイラ,リンカ,エディタなどを含む開発環境(S5 Integrated Development Environment),評価用ボード,自社開発のBIOSなどを用意する.OSとして,米国MontaVista Software社の「MontaVista Linux」をサポートする.

内蔵するインターフェース回路の構成が異なる3品種を用意する.まず,PCI-XやギガビットEthenetのインターフェース回路を備える通信/ネットワーク市場向けの「S5610」を,2004年7月に出荷する予定.

[図1] S5 Engineの構成

[表1] S5000ファミリの概要

型名

S5400

S5500

S5610

CPUコア

S5

S5

S5

DDR SDRAMインターフェース

DDR-333,32ビット

DDR-400,64ビット

DDR-400,64ビット+ECC(error correcting code)

内蔵SRAMの容量

256Kバイト

256Kバイト

256Kバイト

PCIインターフェース

32ビットPCI(33MHz)

32ビットPCI(66MHz)

PCI-X

SysADバス幅

-

-

64ビット

Ethernet

10M/100M Ethernet

10M/100M Ethernet×4

10M/100M/ギガビットEthenet×4

出荷開始時期

2004年11月

2004年9月

2004年7月

応用分野

家電機器,マルチメディア機器,ワイヤレス機器

医用電子装置,OA機器,放送用機器

通信機器,ネットワーク機器,軍用電子機器

■価格 |

■連絡先 |