[ keyword: 開発環境 ]

Aldec,ソフト・マクロCPUを組み込んだFPGA向けのハードウェア・ソフトウェア協調検証環境を発売

ニュース 2003年10月24日

米国Aldec社は,ソフト・マクロCPUを組み込んだFPGA向けのハードウェア・ソフトウェア協調検証環境「CoVer」を発売した.対応するソフト・マクロCPUは,米国Altera社の「Nios」と米国Xilinx社の「MicroBlaze」.ソフト・マクロCPUとは,HDLデータの形で提供されるマイクロプロセッサのIPコアである.論理合成や配置配線はユーザ側で実施する必要がある.

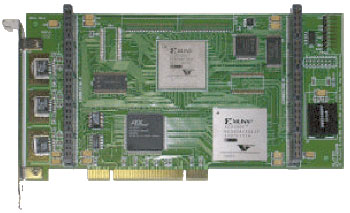

本検証環境は,Altera社またはXilinx社のFPGA,およびSDRAMなどが搭載されたPCIボード「CoVerボード」,HDLシミュレータ「Active-HDL」,GNUのC/アセンブリ・コード・デバッガ「GDB」から構成される.CoVerボードをパソコンに組み込み,パソコン上で稼働するHDLシミュレータやC/アセンブリ・コード・デバッガと協調動作させる.

ソフト・マクロCPUやオンチップ・バスなどのHDLモデルは,あらかじめCoVerボード上のFPGAにマッピングされている.それ以外の回路(CPUの周辺回路やユーザ論理など)のHDLモデルはHDLシミュレータ上で動作させる.ソフト・マクロCPUの制御ソフトウェア(組み込みソフトウェア)は,CoVerボードのFPGAに転送して実行する.CPUの周辺回路やユーザ論理のデバッグにはHDLシミュレータを,制御ソフトウェアのデバッグにはGDBを利用する.ハードウェアとソフトウェアのどちらについても,ブレーク・ポイントの設定やステップ実行を行える.

CPUコアの部分をHDLモデルによるシミュレーションで処理しようとすると,多くのメモリが必要になり,また,検証速度がかなり遅くなる.そこで,CPUコアをFPGAに実装して検証速度の向上を図った.例えば,MicroBlazeを組み込んだFPGAの場合,16MHzの動作クロックに合わせて検証できるという.

[写真1] CoVerボードの外観(Virtex-II XC2V1000と64MバイトのSDRAMを搭載)

■価格 |

■連絡先 |