[ keyword: I/F ]

NEC,面積を従来の約1/10に,消費電力を約1/3に削減した伝送速度10Gbpsのシリアル通信向けCDRマクロセルを開発

ニュース 2003年3月7日

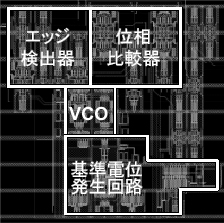

NECは,面積を従来の約1/10に,消費電力を約1/3に削減した伝送速度10Gbpsのシリアル通信向けCDR(clock data recovery)マクロセルを開発した.CDRとは,高速なシリアル通信において,受信信号からクロック信号とデータ信号を抽出する回路である.0.15μmルールのCMOSプロセスで試作したところ,試作チップのダイ・サイズは120μm×130μmに,消費電力は50mWになったという.

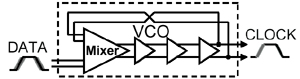

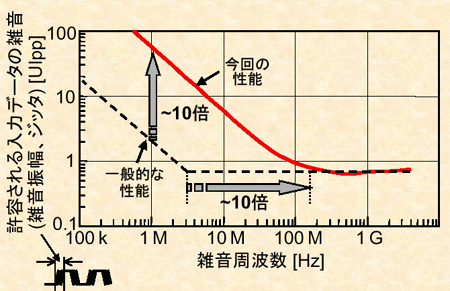

従来のCDRは,クロック信号を生成するVCO(電圧制御発振器)と,このクロック信号と受信信号の同期を取るためのフィードバック制御回路および遅延回路から構成されていた.今回開発したCDRでは,VCOに受信信号を直接入力するだけで,受信信号とVCO出力の同期をとれるようにした.ミキサ回路を使って受信信号とVCO出力の位相制御を行いながら同期をとっており,フィードバック制御回路や遅延回路などは使用していない.また,従来と比べてノイズ耐性を約10倍に引き上げることができたという.このほか,発振波形をモニタする回路を追加した.これによって,発振波形を補正できるようになった.

ハイエンドのサーバやルータなどでは,今後,シリアル通信の多チャネル化とデータの大容量化が進むもよう.そのためトランシーバ回路などの規模が増大し,その消費電力が問題になるという.また,複数のトランシーバ回路を搭載することによって,お互いが相手のノイズ源になるといった問題も発生する.同社では,本マクロセルの使用がこれらの対策の手段の一つになる考えている.

[図1] 試作したCDRのVCO部のブロック図

[図2] 試作したCDRのノイズ耐性

[写真1] 試作したCDRチップのダイ・マップ

■連絡先 |