[ keyword: EDA ]

レグラス,LSIテスタ機能を内蔵するASIC向け機能検証用装置を発売

ニュース 2002年6月5日

レグラスは,LSIテスタ機能を内蔵する機能検証用装置「EVA-SITE」を発売する.動画処理や通信処理など,リアルタイム性を要求されるIPコアやASICの検証・評価に利用できる.同社とトライテックが共同で開発した.

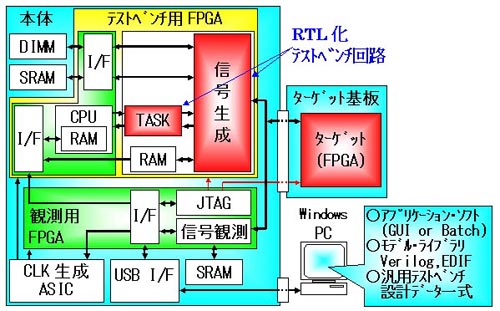

EVA-SITEは,論理LSIのRTL設計時に作成するテストベンチをハードウェア化(米国Altera社の大規模PLDにマッピング)する装置である.このハードウェアが生成した実信号をターゲット・ボード(例えばFPGAボードやブレッド・ボード)に入力する.また,クロック生成回路を備えており,最大5系統のクロックをターゲット・ボードに入力できる.ターゲット・ボードから出力される信号は,再びEVA-SITEに取り込まれる.取り込んだ信号の波形は,USBケーブルを介してEVA-SITEに接続されたパソコンで動作するHDLシミュレータ(米国Mentor Graphics社のModelSim)の波形表示画面上で確認することができる.なお,ターゲット・ボードについては,レグラスが提供するFPGAボードを利用するか,別途ユーザが用意する必要がある.

EVA-SITEは最大50MHzのシステム・クロックで動作するという.I/O数は最大320.また,512MバイトのDIMMと512KバイトのSRAMを内蔵する.テストベンチの記述言語はVerilog HDL.生成するクロックの周期は1.0nsステップで,立ち上がり/立ち下がりの位相は0.1nsステップで制御できる.ターゲット・ボードの出力信号を観測する際のストローブ本数は任意.ストローブ位置は0.1nsステップで設定できる.EVA-SITEに取り込まれた信号はVCD(value change dump)フォーマットに変換されてからパソコンに転送される.

本検証用装置は2002年7月に出荷される予定.

[図1] システム構成

[写真1] EVA-SITE検証システム

■価格 |

■連絡先 |