[ keyword: LSI ]

MentorがATPGとBISTを併用してテスト・パターン量を従来の1/10に削減する技術を製品化

ニュース 2001年10月2日

米国Mentor Graphics社は,ATPG(automatic test pattern generation)とBIST(built-in self-test)を併用して,テスト対象となるチップ(DUT:device under test)に入力するテスト・パターン量を従来の1/10に削減する技術「Embedded Deterministic Test」を開発した.また,この技術を採用したテスト設計用ソフトウェア「TestKompress」を発売する.テスト・パターン量が減るとテスト時間が短くなるので,全体のテスト・コストを削減できる.

本手法では,まず,ATPGツールを使って,テスト・パターンを生成する.このとき,LSIテスタからチップに与える入力チャネル数が減少するように,テスト・パターンのデータ圧縮を行う.

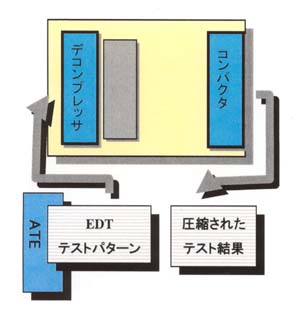

DUTについては,従来のBIST手法と同じように,あらかじめテスト専用回路(デコンプレッサ回路,コンパクタ回路)を埋め込んでおく.LSIテスタのプローブからDUTに送られた圧縮済みのテスト・データは,デコンプレッサ回路に転送される.ここでテスト・データが展開され,ATPGツールで生成されたものと同等のパターンに変換される.展開されたテスト・パターンは,フルスキャン方式の場合と同じように,スキャン・チェーンへ送られる.なお,ここで展開されるテスト・パターンは,通常のテスト・パターンと比べて,データ量がかなり大きくなる.そのため,一般にスキャン・チェーン数は増加し,1本のスキャン・チェーンの長さは短くなる.

一方,テスト結果のパターンは順次コンパクタへ転送され,出力チャネル数が減少するように圧縮されて,出力ピンからLSIテスタへ送られる.

従来のBIST手法では,疑似ランダム・パターン発生回路を利用して,チップ内部でテスト・パターンを自動生成する.疑似ランダム・パターンを利用すると,故障検出率が上がりにくいという欠点がある.これに対して本手法では,ATPGツールで生成したものと同等のパターンをチップ内部に送り込むことになる.そのため,故障検出率低下の問題は発生しない.

Embedded Deterministic Testとほぼ同じ技術は,米国IBM社も発表している.IBM社はこの技術を「SmartBIST」と呼んでいる.SmartBISTでは,テスト結果のデータ圧縮にOPMISR(On-Product multiple input signature register)と呼ぶ回路を利用している.OPMISERでは,複数のスキャン・チェーンから転送されたパターンのXORを取っている.そのため,OPMISERにX(不定値)が入力されると,DUTの良否判定が行えなくなるという問題がある(現状では,「Xの伝搬禁止」という制約を設けて回路を設計している).Embedded Deterministic Testではこうした手法を利用しておらず,Xが伝搬しても問題ないという.なお,IBM社も上記のXのビットをマスクする回路を追加するなどして,この問題を回避することを検討しているという.

TestKompressは,2001年第4四半期に出荷を開始する.

[図1] Embedded Deterministic Testの概要

■価格 |

■連絡先 |