[ keyword: SOC ]

ブラックボックスからLEF/DEF,GDS IIまで,多様な回路ブロックを読み込めるデザイン・プランナが日本上陸

ニュース 2001年8月29日

カナダのIcinergy Software社は,ブラックボックスの回路ブロックから,RTLデータ(VHDLやVerilog HDL),ゲート・レベルのネットリスト,フロアプラン・データ(LEF/DEF),マスク・データ(GDS II)まで読み込めるデザイン・プランニング・ツール「SOCarchitect」の国内での販売を開始した.デザイン・プランニング・ツールとは,チップ面積やタイミングなどを見積もりながら,チップ上の最適なフロアプラン(回路ブロックの概略配置)を決定する工程を支援するEDAツールである.LSI設計の比較的早い段階(たとえば,概念設計やアーキテクチャ設計,RTL設計などの工程)で使用される.

既存のデザイン・プランニング・ツールでは,対応する設計データのフォーマットの種類が限られていたという.そのため,ユーザはツールがサポートするフォーマットの設計データを用意するため,かなりの労力を費やしていた.一方,SOCarchitectの場合,例えばまだ仕様が確定していない回路ブロックに対して,おおよそのゲート数とゲート利用率をユーザが指定すると,チップ上にブラックボックスの回路ブロックが自動生成される.

SOCarchitectは,回路ブロックの自動配置機能とブロック間配線(グローバル配線)機能を備えている.チップ面積,ブロック間の配線長,配線混雑度,消費電力などの制約を考慮して最適なフロアプランを生成する.例えば,発熱しやすいメモリなどは自動的に分散して配置するという.このほか,回路ブロックのポート(端子)割り付け,I/Oパッドの配置,階層分割,PDFフォーマットのドキュメント(データシート)生成といった機能を備えている.また,レイアウト設計ツール用のLEF/DEFデータやPDEFデータのほか,米国Synopsys社の論理合成ツール(Design Compiler)用のワイヤ・ロード・モデル(set_load)なども出力する.なお,SOCaricitectには論理合成や静的タイミング解析(STA:static timing analysis)の機能は含まれていない.

対応しているOSは,Solaris,Linux,Windows98/NT/2000.なお,SOCarchitectは,旧Cooper & Chan Technology社や旧UniCAD社のスタッフが中心となって開発したという.Icinergy社の共同創設者には,業界標準の自動配線ツール「SPECCTRA」を開発したJohn Cooper氏が含まれている.

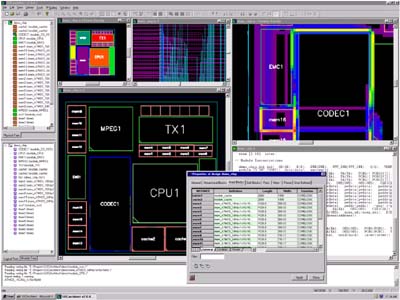

[図1] SOCarchitectの画面例1

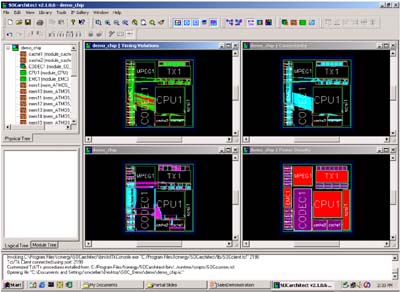

[図2] SOCarchitectの画面例2

■価格 |

■連絡先 |