あなたの作ったテストベンチのバグ検出能力を高める方法 ―― ミューテーション法を利用した検証環境の品質改善

3.機能検証環境の品質改善の例

ここでは米国SpringSoft社のツールである「Certitude」を例に,機能検証環境の品質改善について説明します.Certitudeは,検証工程において深刻なRTLバグのすり抜けを引き起こす「穴(hole)」を「フォールト(fault;欠陥)」を挿入することで検出し,修正することで,高品質なICを実現します.

Certitudeは,「自社開発のIPコア(再利用可能な大規模回路ブロック)の検証手法」や「サード・パーティ製IPコアの品質保証の方法」,「SoC(System on a Chip)の検証環境の品質」などを改善するために利用します.それぞれの適用方法について,順番に説明していきます.

●自社で開発したIPコアの検証手法を改善

多くの企業は,設計・検証戦略の重要な要素の一つとして,高品質のIPコアの自社開発を考えます.たいていの場合,こうした自社開発のIPコアにはその企業独自の機能や特徴が含まれており,多くのSoC設計で再利用され,企業の成功に貢献しています.ミューテーション・ベースの技術を使用すれば,このようなIPコアの検証を早期に完了することができます.

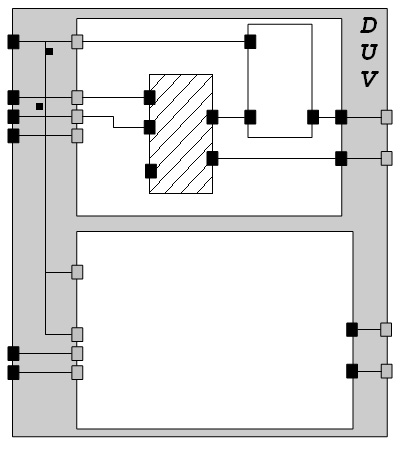

自社製IPコアの開発チームは,検証工程の早い段階でCertitudeを使用し,優先度の高いフォールト(重要度の高い検証項目に対応)を挿入して検証環境の品質を評価します(図5).そして,ここで得た結果を踏まえて検証環境を強化し,さらなる検証を行う際の参考にします.検証環境の品質が改善されたら,検証項目の優先順位を考慮しながら,別のフォールトを挿入します.このような作業を繰り返すことで,検証環境全体の品質を評価・改善できます.

(a) 接続性フォールト(入出力ポートの固定や反転)

(b) RTLフォールト

図5 フォールトの種類

このような過程を経て検証環境の品質を改善した後,統計的なフォールトのサンプルを使って,この検証環境が潜在的なバグをどの程度,検出できるかを計算することも可能です.この数値は,設計変更によって検証環境の品質が低下していないかどうかを確認するためにも利用できます.また,IPコアがSoCの開発チームに提供される際に,サインオフ項目の一部として利用することもできます.

●サード・パーティ製IPコアの品質保証に有効

外部から調達したIPコアの品質保証は,頭の痛い問題です.IPコアの中の不具合をSoCへ統合する工程やその検証工程でデバッグすることは非常に難しく,また,その際のエンジニアリング・コストは高く,最悪の場合,プロジェクトが遅延したり,設計の手戻りが生じます.

IPコアがRTLのソース・コードで提供され,サインオフのテスト環境が用意されている場合,ミューテーション・ベースの技術はテスト環境の品質評価やSoCへ統合する過程で生じうる潜在的な問題の発見に役立ちます.最終的にIPコアを受け取る設計者はRTLコードの内部動作の知識を持たないため,IPコアの評価では通常,自社開発のIPコアの場合と同じように統計的なフォールトのサンプルを使用します.この評価によって問題点が見つかると(おそらくそれは,自社開発のIPコアの場合に見つかった問題点とは異なる),品質保証のために追加の検証が必要になります.極端な例では,再度検証した結果,別のIPベンダを探さなければならなくなったり,あるいはIPベンダの選定基準を見直さなければならなくなります.

これと同じような手法が,新規設計の中の再利用可能な回路ブロックの品質評価に利用されます.統計的なフォールトのサンプルを利用して評価することにより,追加の検証が必要な回路ブロックを迅速に特定できます.あるいは,少なくともSoCへ統合する工程やその検証工程で注意を払う必要のある領域が明らかになります.

●SoCの検証環境の品質を改善

通常,設計の規模や複雑さが増大することは,SoCの検証のあらゆる側面で制約となります.一般に,Correct-by-Construction(構築しながら,逐次修正を行う)手法を用いるか,もしくは大規模なサーバ・センタを利用して複数のシミュレーションを並行して実行することで,この問題に対処します.ミューテーション・ベースの技術も同じで,どのような手順や方法で実施するかがポイントとなります.

実績のある最良のアプローチは,自社開発のIPコアの検証手法のところで述べた手法を利用して,回路ブロックの検証環境の品質をチェックする方法です.優先度が高いフォールトから順番に適用して,検証環境の品質を逐次改善していきます.SoCを構築する上で基盤となる高品質のIPコアを実現するには,検証環境の品質を安定させることが基本となります.

IPコアの品質が高まれば,設計者はSoCの検証工程において,ブロック間インターフェースや最上位階層のI/Oの検証に注力できます.Certitudeでは,このような領域を評価するための接続性フォールト(connectivity fault)の専用クラスが定義されており,既存の環境の検証の品質をチェックできます.この段階では,ブロック間の通信プロトコルやI/O信号処理に関連した深刻な不具合が隠れている可能性があります.大規模なLSIの設計においてミューテーション・ベースの技術を用いれば,少数のフォールトの挿入によって検証環境の品質を高め,現実的な時間で検証できるようになります.

●参考URL

(1) SpringSoft,Functional qualification: a technical brief.

George Bakewell

米国SpringSoft社,プロダクト・マーケティング担当ディレクタ

◆筆者プロフィール◆

George Bakewell.高機能検証システムのプロダクト・マネージメントと技術的方向性の決定を担当.新たな要求や仕様に対して,製品開発チームと緊密に連携して活動してる.技術会議における講演,業界の標準化組織のメンバとしての活動,技術チュートリアルやアプリケーション・ワークショップを行っている.20年以上にわたるEDA業界での経験があり,コロラド大学で電子工学/コンピュータ・サイエンスの学士号を取得している.