無償ツールで実践する「ハード・ソフト協調検証」(7) ―― DMAの割り込み機能を確かめられるようにする

無償のSystemVerilog対応シミュレータと無償のFPGA用オンチップ・バス・モデルを用いて,ハードウェア・ソフトウェア協調検証の一手法について解説する連載の第7回である.今回は,CPUモデルに割り込み入力信号と割り込みタスクを追加する.これにより,DMAの割り込み機能を確認できるようになる.また,検証に利用したテスト・プログラムとシミュレーションの結果も示す.(編集部)

技術解説シリーズ「無償ツールで実践する『ハード・ソフト協調検証』」 |

18.割り込みに対応する

●CPUモデルに割り込みを追加する

ライブラリ化したCPUモデルは割り込みに対応していないので,SOPC BuilderのライブラリであるDMAやSG-DMA(Scatter-Gather DMA)の割り込み機能を確かめることができません.そこで,ここではCPUモデルに割り込みを追加していきます.

CPUモデル(avalon_cpu.sv)に追加するのは,

- 割り込み入力信号 irq[31:0]

- 割り込みタスク wait_for_interrupt( output int unsigned status )

です.

リスト12にモジュール(avalon_cpu)のポート部を示します.

リスト12 モジュールのポート部

module avalon_cpu ( input wire clk, input wire [31:0] irq ); |

ポート部の最後に,入力信号として32ビット幅の割り込み線(irq)を追加します.

次に割り込みタスク(wait_for_interrupt( output int unsigned status ))をリスト13に示します.

リスト13 割り込みタスク(wait_for_interrupt)

| task wait_for_interrupt( output int unsigned status ); status = 0; endtask : wait_for_interrupt |

wait_for_interruptタスクは,割り込み線(irq)が0(ゼロ)以外になるまでウェイトし,statusにirqの値を返します.そして,C言語のテスト・プログラム側から呼び出せるようにexport宣言します.

| export "DPI-C" task wait_for_interrupt; |

ポート(irq)を追加したので,SOPC Builderのライブラリを編集します.SOPC Builderを立ち上げ,Libraryにある「avalon_cpu」を右クリックし,メニューの「Edit」を選択します.するとComponent Editorが表示されるので,HDL Filesペインを選択します(図27).[Reanalyze HDL Files]ボタンをクリックし,avalon_cpu.svの再読み込みを行います.

図27 Component Editorでavalon_cpu.svを再読み込みを行う

再読み込みでエラーが発生しなかったら,[Next]ボタンをクリックします.エラーが発生したら,追加および修正した箇所が正しいかどうかを確認してください.

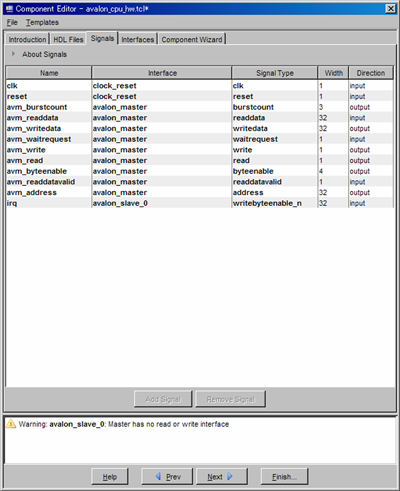

Signalsペインが表示されるので,最後の行に割り込み線(irq)が追加されていることを確認します(図28).

図28 割り込み信号(irq)の割り当てを行う

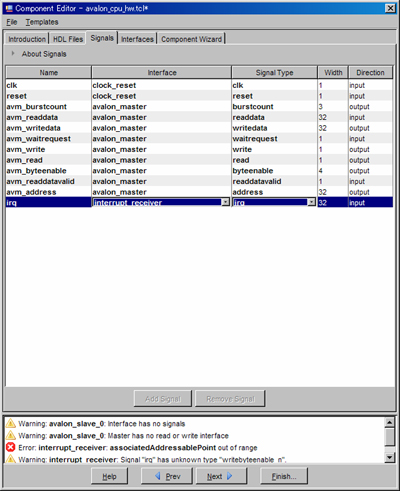

そして,irqのInterfaceを「avalon_slave_0」から「new Interrupt Receiver」に,SignalTypeを「writebyteenable_n」から「irq」に変更します(図29).

図29 irqのInterfaceとSignalTypeを変更する

[Next]ボタンをクリックすると,Interfaceペインが表示されるので,[Remove Interfaces With No Signals]ボタンをクリックします(図30).

図30 割り込みのインターフェース部分

それから"interrupt_receiver"のParameters部のAssociated addressable interfaceを「none」から「avalon_master」に変更します(図31).

図31 Associated addressable interfaceを「none」から「avalon_master」へ変更

最後に[Finish]ボタンをクリックし,Save Changesウィンドウが表示されたら,[Yes, Save]ボタンをクリックして終了します.すると,右側のcpuのBase部に IRQ 0が,End部に IRQ 31 が表示されて,割り込みがサポートされたことが分かります.