FPGAのタイミング・エラーとその対処

鈴木 量三朗 Ryozaburo Suzuki

一般的に配置配線でタイミング・エラーが発生した場合は、パイプライン段数を増やすなどソース・コードを修正して対応することが多いでしょう。しかしソース・コードが提供されていないIPコアを使っている場合など、ソース・コードを修正できない場合は、配置配線ツールにさまざまなオプションを指定し、条件を変えて配置配線を何度も試してみるしかありません。ここではFPGAデザイン最適化ツールである InTime を使って、タイミングをミートさせる事例について紹介します。

図1 配置配線でエラーが発生!

## Vivado のタイミング・エラー

## ● 配置配線でエラーが発生!

高位合成やRTL設計が終わり、いざ論理合成そして配置配線でFPGAに実装してみると、タイミングに関連するエラー(バイオレーション)が発生するということはよくあります。図1はVivadoでImplementaionした直後に「Failed Timing!」とバイオレーションが出てしまった例です。赤文字で-1542.872nsと表示され、あまりにも大きい値である

ため、これを見た瞬間に絶望的になってしまうかもし れません。

とはいえ、遅延にしてはあまりにも大きい値です.これはいったい何を指し示しているのでしょうか?

## ● デザインの説明

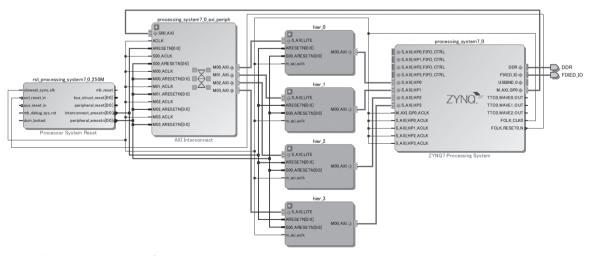

ここでは、簡単なBRAM (FPGA内蔵のRAM)を使用したデザインを例に、タイミング・エラーについて説明します(図2).このデザインには入出力はないものの、画像処理で行われる典型的なデザインを模しています。つまり、外部メモリからBRAMに転送し、なんらかの処理をしてまた、外部メモリへ書き戻すようなケースです。ここでは「なんらかの処理」は省かれていますが、こういったBRAMメモリの扱い方は画像処理では一般的です。

その結果として何が起こるかというと、BRAMに 処理が集中することになります。BRAMをアクセス する近辺での配線の集中は、回路が迂回されるなどの 問題が生じやすいためタイミング・バイオレーション を誘発生しやすいデザインになります。

## Vivadoのエラー関連略号

改めて、Vivadoで配置配線後にProject Summary

図2 例題としてBRAMを使ったデザイン