# FPGA内蔵ロジック・アナライザ機能の基礎と応用 Nios II と自作周辺回路の ハード&ソフト混在デバッグ

小林優 Masaru Kobayashi

今回はFPGA評価ボードDEOを用いて、ソフト・コアCPU「Nios II」に自作周辺回路を付加したシステムの検証を行ってみます。不具合の原因が周辺回路のハードウェアなのか、制御するソフトウェアなのか判別するためには、FPGA内蔵ロジック・アナライザ機能「SignalTap II」の利用が欠かせません。Nios IIのデバッグ環境Nios II EDS (Embedded Design Suit) も使うので手順が少々複雑です。最初にバスの動作を確認し、続いて応用的な機能を使った波形観測も行ってみます。

## 1

### Nios IIシステムに 文字表示回路を接続

#### システムの概略

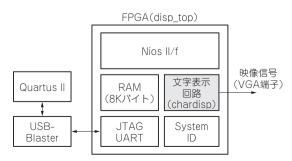

今回波形観測するシステムは**図1**に示した構成になっています. その概略は次の通りです.

• Nios II/f : ソフト・コア・プロセッサ

・8KバイトRAM:プログラムおよびデータ格納

• JTAG UART : JTAGを経由したシリアル通信

• System ID : ハードウェアのバージョン識別 以上はシステム統合ツール Qsysに用意された周辺 回路 (IP) です. Nios II を動作させるための最小限の システムにしました.

これに自作の周辺回路である文字表示回路(chardisp)を接続しました。この回路では、PC用のディスプレイに縦横8ドットで構成した英数字を表示できます。横80文字縦50行が表示でき、また1文字ごとに独立して色を指定できます。

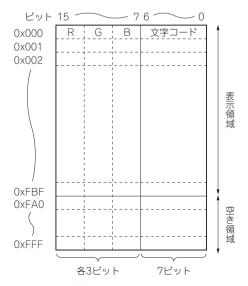

内部に文字色と文字コードを格納するVRAM(ビデオRAM)を持ち(図2)、CPU側から値を書き込むことで、画面の任意の位置に任意の文字を任意の色で表示できます。DEOボードのVGA出力はRGB各色4ビットの簡易D-Aコンバータを備えていますが、本回路では各色3ビットとしました。1文字を16ビットで表現することでFPGA内蔵メモリを効率良く使うためです。

図1 検証で用いた Nios II システム

#### ■ Avalonバスに自作回路を接続

文字表示回路は、Nios IIのAvalonバスに接続します。表1に示すように非常に単純なバスで、

- ・クロック同期(立ち上がりで動作)

- writeが1ならaddressで指定した箇所にwritedata の値を次クロックで書き込む

- read が1なら address で指定した箇所のデータを readdataに出力すると次クロックでCPUが読み込む となっています. read やwrite 信号は、上位アドレス のデコードを含んで作成されているので、接続したブロック専用の読み書き信号として使えます.

#### 文字表示回路の詳細

文字表示回路の詳細ブロック図を図3に示します. CPUからはVRAMを直接読み書きできます.データのバス幅は16ビットとなり、2ビットのbyte enable 信号で上位/下位バイトを独立して読み書きできます. VRAMは読み書きが独立して行える簡易的なデュアルポート構成です. 読み書きそれぞれに1クロック

図2 VRAMの構成